### **General Description**

The MAX1513/MAX1514 provide complete power-supply solutions for active-matrix thin-film transistor (TFT) liquid-crystal displays (LCDs). Both devices include a high-performance step-up regulator controller, three linear-regulator controllers, and an adjustable delay block for startup sequencing. The MAX1513 includes an additional linear-regulator controller and a high-performance buffer amplifier. The MAX1513/MAX1514 can operate from 2.7V to 5.5V input supplies and provide overload protection with timer delay latch on all the regulated outputs.

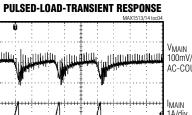

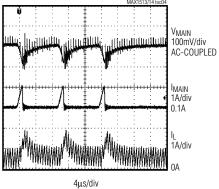

The step-up regulator controller drives an external Nchannel MOSFET to generate the regulated supply voltage for the panel source-driver ICs. Its current-mode control architecture provides fast transient response to pulsed loads. The high switching frequency (up to 1.5MHz) allows the use of ultra-small inductors and ceramic capacitors while achieving efficiencies over 85% using lossless current sensing. The internal soft-start limits the input surge current during startup.

The gate-on and gate-off linear-regulator controllers of the MAX1513/MAX1514 provide regulated TFT gate-on and gate-off supplies. The gate-on supply is activated after an adjustable delay following the step-up regulator. The logic linear-regulator controller can be used to create a low-voltage logic supply. The gamma linear-regulator controller of the MAX1513 can be used to generate a gamma-correction reference supply or another generalpurpose supply rail. The MAX1513's high-performance buffer amplifier can drive the LCD backplane (VCOM) or the gamma-correction divider string.

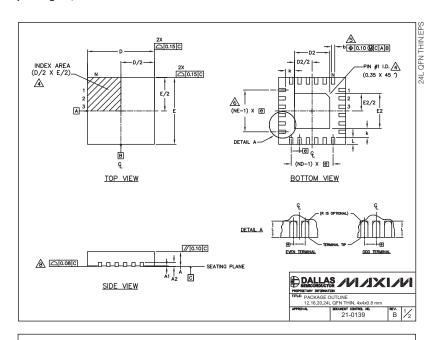

The MAX1513/MAX1514 are available in 4mm x 4mm 20-pin thin QFN packages with a maximum thickness of 0.8mm, suitable for ultra-thin LCD panel design.

### **Applications**

Notebook Computer Displays LCD Monitors and TVs **Automotive Displays**

Pin Configuration appears at end of data sheet.

### **Features**

- ♦ 2.7V to 5.5V Input Supply Range

- ♦ Input-Supply Undervoltage Lockout

- **♦ Current-Mode Step-Up Controller Fast Transient Response to Pulsed Load High Efficiency Lossless Current Sensing** 430kHz/750kHz/1.5MHz Switching Frequency

- ♦ Linear-Regulator Controllers for Vgon, Vgoff

- **♦** Linear-Regulator Controller for Logic Supply

- ♦ High-Performance Buffer Amplifier (MAX1513 Only)

- **♦** Additional Linear-Regulator Controller (MAX1513 Only)

- ♦ Power-Up Sequence and VGON Delay Control

- ♦ VMAIN, VGON, VGOFF, VGAMMA Shutdown Control

- ◆ Timer-Delay Fault Latch for All Outputs

- Thermal-Overload Protection

### **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE           |

|------------|----------------|-----------------------|

| MAX1513ETP | -40°C to +85°C | 20 Thin QFN 4mm x 4mm |

| MAX1514ETP | -40°C to +85°C | 20 Thin QFN 4mm x 4mm |

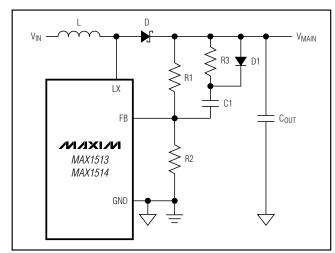

### **Minimal Operating Circuit**

Maxim Integrated Products 1

### **ABSOLUTE MAXIMUM RATINGS**

| FB, FBP, FBN, FBG, FBL, IN, CS- | <b>+</b> ,                              |

|---------------------------------|-----------------------------------------|

| CS-, SDFR to GND                | 0.3V to +6V                             |

| DEL, GATE, REF to GND           | 0.3V to $(V_{IN} + 0.3V)$               |

| SUPB to GND                     | 0.3V to +14V                            |

| OUTB, FBPB to GND               | 0.3V to (V <sub>SUPB</sub> + 0.3V)      |

| DRVP, DRVG, DRVL to GND         | 0.3V to +30V                            |

| DRVN to GND                     | ( $V_{IN}$ - 28V) to ( $V_{IN}$ + 0.3V) |

| OUTB Continuous Output Current                        | .±75mA  |

|-------------------------------------------------------|---------|

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |         |

| 20-Pin TQFN (derate 16.9mW/°C above +70°C)1           | 349mW   |

| Operating Temperature Range40°C to                    | o +85°C |

| Junction Temperature                                  | +150°C  |

| Storage Temperature Range65°C to                      |         |

| Lead Temperature (soldering, 10s)                     | +300°C  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 1,  $V_{IN} = 3V$ ,  $V_{SUPB} = 10V$ ,  $\overline{SDFR} = IN$ ,  $C_{REF} = 0.22 \mu F$ ,  $T_A = 0^{\circ}C$  to +85°C. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                       | SYMBOL           | CONDITIO                                                                | ONS                            | MIN   | TYP                    | MAX   | UNITS |

|---------------------------------|------------------|-------------------------------------------------------------------------|--------------------------------|-------|------------------------|-------|-------|

| IN Supply Range                 | VIN              |                                                                         |                                | 2.7   |                        | 5.5   | V     |

| IN Undervoltage-Lockout         | \/. n # 0        | 250mV typical byotorogic                                                | V <sub>IN</sub> rising         | 2.5   | 2.7                    | 2.9   | V     |

| Threshold                       | Vuvlo            | 350mV typical hysteresis                                                | V <sub>IN</sub> falling        | 2.2   | 2.35                   | 2.5   | \ \   |

| IN Quiescent Current            | I <sub>IN</sub>  | V <sub>FB</sub> = V <sub>FBP</sub> = V <sub>FBL</sub> = V <sub>FB</sub> | G = 1.5V, V <sub>FBN</sub> = 0 |       |                        | 1.25  | mA    |

| IN Shutdown Current             |                  | $V_{\overline{SDFR}} = 0$ , $V_{\overline{FBL}} = 1.5V$                 |                                |       |                        | 150   | μΑ    |

| REF Output Voltage              |                  | $-2\mu A < I_{REF} < 100\mu A, 2.7$                                     | $V < V_{IN} < 5.5V$            | 1.231 | 1.250                  | 1.269 | V     |

| Thermal Shutdown                |                  | Temperature rising                                                      |                                |       | +160                   |       | °C    |

| Thermal Shutdown                |                  | Hysteresis                                                              |                                |       | 15                     |       | 10    |

| Duration to Trigger Fault Latch |                  |                                                                         |                                |       | 43.6                   |       | ms    |

| MAIN STEP-UP CONTROLLER         |                  |                                                                         |                                |       |                        |       |       |

|                                 |                  | SDFR = IN                                                               |                                | 1.275 | 1.500                  | 1.725 |       |

| Operating Frequency             | fosc             | SDFR = REF                                                              |                                | 0.60  | 0.75                   | 0.90  | MHz   |

|                                 |                  | SDFR = unconnected                                                      |                                |       | 0.43                   |       |       |

| Oscillator Maximum Duty Cycle   |                  |                                                                         |                                | 80    | 85                     | 90    | %     |

| FB Regulation Voltage           | V <sub>FB</sub>  | $V_{CS+} - V_{CS-} = 0$                                                 |                                | 1.237 | 1.25                   | 1.263 | V     |

| FB Fault Trip Level             |                  | V <sub>FB</sub> falling                                                 |                                | 0.96  | 1.00                   | 1.04  | V     |

| FB Load Regulation              |                  | $0 < (V_{CS+} - V_{CS-}) < 50 \text{mV}$                                | 1                              |       | -1                     |       | %     |

| FB Line Regulation              |                  | $V_{IN} = 2.7V \text{ to } 5.5V$                                        |                                |       | 0.1                    | 0.2   | %/V   |

| FB Input Bias Current           |                  | $V_{FB} = 1.5V$                                                         |                                | -100  |                        | +100  | nA    |

| CS+ Input Current               |                  | 2.2V < V <sub>CS+</sub> < 6V                                            |                                |       |                        | 90    | μΑ    |

| CS- Input Current               |                  | 2.2V < V <sub>CS</sub> - < 6V                                           |                                | -1    |                        | +1    | μΑ    |

| Current-Limit Threshold         |                  | V <sub>CS+</sub> - V <sub>CS-</sub> , 2.2V < V <sub>CS+</sub>           | < 6V                           | 100   | 125                    | 150   | mV    |

| Gate-Drive Output               |                  | High or low                                                             |                                |       | 3                      | 5     | Ω     |

| Soft-Start Period               | tss              |                                                                         |                                |       | 2.7                    |       | ms    |

| Soft-Start Step Size            |                  |                                                                         |                                |       | V <sub>REF</sub> / 128 |       | V     |

| GATE-ON LINEAR-REGULATO         | R CONTROI        | LLER (REG P)                                                            |                                |       |                        |       |       |

| FBP Regulation Voltage          | V <sub>FBP</sub> | IDRVP = 50µA                                                            |                                | 1.225 | 1.250                  | 1.275 | V     |

| FBP Fault Trip Level            |                  | V <sub>FBP</sub> falling                                                |                                | 0.96  | 1.00                   | 1.04  | V     |

| FBP Input Bias Current          |                  | V <sub>FBP</sub> = 1.5V                                                 |                                | -250  |                        | +250  | nA    |

\_\_ /VIXI/VI

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{IN} = 3V$ ,  $V_{SUPB} = 10V$ ,  $\overline{SDFR} = IN$ ,  $C_{REF} = 0.22 \mu F$ ,  $T_A = 0^{\circ}C$  to +85°C. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                                                 | SYMBOL                                       | CONDITIONS                                                    | MIN   | TYP                    | MAX   | UNITS |

|-----------------------------------------------------------|----------------------------------------------|---------------------------------------------------------------|-------|------------------------|-------|-------|

| FBP Effective Load-Regulation Error (Transconductance)    |                                              | V <sub>DRVP</sub> = 10V, I <sub>DRVP</sub> = 25μA to 500μA    |       | -1.5                   | -2    | %     |

| FBP Line (IN)-Regulation Error                            |                                              | I <sub>DRVP</sub> = 50µA, 2.7V < V <sub>IN</sub> < 5.5V       |       |                        | 8     | mV    |

| DRVP Sink Current                                         | I <sub>DRVP</sub>                            | V <sub>FBP</sub> = 1.1V, V <sub>DRVP</sub> = 10V              | 1     |                        |       | mA    |

| DRVP Off-Leakage Current                                  | Off-Leakage Current VFBP = 1.5V, VDRVP = 28V |                                                               |       | 0.15                   | 10    | μΑ    |

| DEL Charge Current                                        |                                              | During startup, V <sub>DEL</sub> = 1.0V                       | 4     | 5                      | 6     | μΑ    |

| DEL Turn-On Threshold                                     | V <sub>TH</sub> (DEL)                        |                                                               | 1.19  | 1.25                   | 1.31  | V     |

| DEL Discharge Switch<br>On-Resistance                     |                                              | V <sub>IN</sub> = 3.0V, V <sub>FB</sub> = 0.8V                |       | 15                     |       | Ω     |

| Soft-Start Period                                         | tss                                          |                                                               |       | 2.7                    |       | ms    |

| Soft-Start Step Size                                      |                                              |                                                               |       | V <sub>REF</sub> / 128 | 3     | V     |

| GAMMA LINEAR-REGULATOR                                    | CONTROL                                      | LER (REG G, MAX1513 ONLY)                                     |       |                        |       |       |

| FBG Regulation Voltage                                    | V <sub>FBG</sub>                             | I <sub>DRVG</sub> = 0.35mA                                    | 1.235 | 1.250                  | 1.265 | V     |

| FBG to FB Regulation Voltage Matching                     |                                              | IDRVG = 0.5mA, V <sub>CS+</sub> - V <sub>CS-</sub> = 0        | -1.2  |                        | +1.2  | %     |

| FBG Fault Trip Level                                      |                                              | V <sub>FBG</sub> falling                                      | 0.96  | 1.00                   | 1.04  | V     |

| FBG Input Bias Current                                    |                                              | V <sub>FBG</sub> = 1.5V                                       | -250  |                        | +250  | nA    |

| FBG Effective Load-Regulation<br>Error (Transconductance) |                                              | V <sub>DRVG</sub> = 10V, I <sub>DRVG</sub> = 0.175mA to 3.5mA |       | -1.5                   | -2    | %     |

| FBG Line (IN)-Regulation Error                            |                                              | I <sub>DRVG</sub> = 0.5mA, 2.7V < V <sub>IN</sub> < 5.5V      |       |                        | 5     | mV    |

| DRVG Sink Current                                         | IDRVG                                        | V <sub>FBG</sub> = 1.1V, V <sub>DRVG</sub> = 10V              | 5     |                        |       | mA    |

| DRVG Off-Leakage Current                                  |                                              | V <sub>FBG</sub> = 1.5V, V <sub>DRVG</sub> = 28V              |       | 0.15                   | 10    | μΑ    |

| Soft-Start Period                                         | tss                                          |                                                               |       | 2.7                    |       | ms    |

| Soft-Start Step Size                                      |                                              |                                                               |       | V <sub>REF</sub> / 128 | 3     | V     |

| LOGIC LINEAR-REGULATOR C                                  | ONTROLLE                                     | ER (REG L)                                                    |       |                        |       |       |

| FBL Regulation Voltage                                    | V <sub>FBL</sub>                             | I <sub>DRVL</sub> = 0.8mA                                     | 1.225 | 1.250                  | 1.275 | V     |

| FBL Fault Trip Level                                      |                                              | V <sub>FBL</sub> falling                                      | 0.96  | 1.00                   | 1.04  | V     |

| FBL Input Bias Current                                    |                                              | $V_{FBL} = 1.5V$                                              | -250  |                        | +250  | nA    |

| FBL Effective Load-Regulation Error (Transconductance)    |                                              | V <sub>DRVL</sub> = 3V, I <sub>DRVL</sub> = 0.4mA to 8mA      |       | -1.5                   | -2    | %     |

| FBL Line (IN)-Regulation Error                            |                                              | I <sub>DRVL</sub> = 1mA, 2.7V < V <sub>IN</sub> < 5.5V        |       |                        | 8     | mV    |

| DRVL Sink Current                                         | I <sub>FBL</sub>                             | V <sub>FBL</sub> = 1.1V, V <sub>DRVL</sub> = V <sub>IN</sub>  | 15    | 20                     |       | mA    |

| DRVL Off-Leakage Current                                  |                                              | V <sub>FBL</sub> = 1.5V, V <sub>DRVL</sub> = 28V              |       | 0.15                   | 10    | μΑ    |

| Soft-Start Period                                         | t <sub>SS</sub>                              |                                                               |       | 2.7                    |       | ms    |

| Soft-Start Step Size                                      |                                              |                                                               |       | V <sub>REF</sub> / 128 | 3     | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{IN} = 3V$ ,  $V_{SUPB} = 10V$ ,  $\overline{SDFR} = IN$ ,  $C_{REF} = 0.22 \mu F$ ,  $T_A = 0^{\circ}C$  to +85°C. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                                                 | SYMBOL            | CONDITIONS                                               | MIN                     | TYP                    | MAX                  | UNITS |

|-----------------------------------------------------------|-------------------|----------------------------------------------------------|-------------------------|------------------------|----------------------|-------|

| GATE-OFF LINEAR-REGULATO                                  | OR CONTRO         | DLLER (REG N)                                            | •                       |                        |                      | •     |

| FBN Regulation Voltage                                    | V <sub>FBN</sub>  | I <sub>DRVN</sub> = 0.2mA                                | 220                     | 250                    | 280                  | mV    |

| FBN Fault Trip Level                                      |                   | V <sub>FBN</sub> rising                                  | 380                     | 420                    | 460                  | mV    |

| FBN Input Bias Current                                    |                   | $V_{FBN} = 0V$                                           |                         |                        | +250                 | nA    |

| FBN Effective Load-Regulation<br>Error (Transconductance) |                   | $V_{DRVN} = -10V$ , $I_{DRVN} = 0.1$ mA to 2mA           |                         | 18                     | 25                   | mV    |

| FBN Line (IN)-Regulation Error                            |                   | I <sub>DRVN</sub> = 0.2mA, 2.7V < V <sub>IN</sub> < 5.5V |                         |                        | 5                    | mV    |

| DRVN Source Current                                       | I <sub>FBN</sub>  | V <sub>FBN</sub> = 0.3V, V <sub>DRVN</sub> = -10V        | 5                       |                        |                      | mA    |

| DRVN Off-Leakage Current                                  |                   | V <sub>FBN</sub> = -0.1V, V <sub>DRVN</sub> = -20V       |                         | 0.1                    | 10                   | μΑ    |

| Soft-Start Period                                         | tss               |                                                          |                         | 2.7                    |                      | ms    |

| Soft-Start Step Size                                      |                   |                                                          |                         | V <sub>REF</sub> / 128 | 3                    | V     |

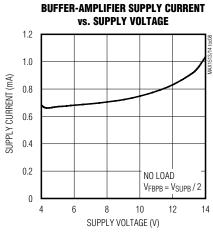

| BUFFER AMPLIFIER                                          | •                 |                                                          | •                       |                        |                      |       |

| SUPB Supply Range                                         | VSUPB             |                                                          | 4.5                     |                        | 13.0                 | V     |

| SUPB Supply Current                                       | I <sub>SUPB</sub> | No load, V <sub>FBPB</sub> = 4V                          |                         | 0.75                   | 1.1                  | mA    |

| FBPB Input Offset Voltage                                 | Vos               | V <sub>FBPB</sub> = V <sub>SUPB</sub> / 2                |                         | 0                      | 12                   | mV    |

| FBPB Input Bias Current                                   | I <sub>BIAS</sub> | V <sub>FBPB</sub> = V <sub>SUPB</sub> / 2                |                         |                        | 50                   | nA    |

| FBPB Input Common-Mode<br>Range                           | Vсм               |                                                          | 0                       |                        | V <sub>SUPB</sub>    | V     |

| Common-Mode Rejection Ratio                               | CMRR              | 0 < V <sub>FBPB</sub> < V <sub>SUPB</sub>                | 50                      |                        |                      | dB    |

| Output-Voltage-Swing High                                 | Voh               | I <sub>OUTB</sub> = 5mA                                  | V <sub>SUPB</sub> - 150 | V <sub>SUPB</sub> -    |                      | mV    |

| Output-Voltage-Swing Low                                  | VoL               | I <sub>OUTB</sub> = -5mA                                 |                         | 80                     | 150                  | mV    |

| Short-Circuit Current                                     |                   |                                                          | ±50                     | ±150                   |                      | mA    |

| Power-Supply Rejection Ratio                              | PSRR              | DC, 6V ≤ V <sub>SUPB</sub> ≤ 13V, V <sub>FBPB</sub> = 4V | 60                      | 80                     |                      | dB    |

| Slew Rate                                                 |                   |                                                          |                         | 10                     |                      | V/µs  |

| -3dB Bandwidth                                            |                   | $R_L = 10k\Omega$ , $C_L = 10pF$                         |                         | 12                     |                      | MHz   |

| CONTROL INPUTS AND OUTPU                                  | JTS               |                                                          |                         |                        |                      |       |

|                                                           |                   | SDFR = IN (1.5MHz operation)                             | $0.9 \times V_{IN}$     |                        |                      |       |

| SDFR Input Level                                          |                   | SDFR = unconnected (430kHz operation)                    | 0.69 × V <sub>I</sub>   | Ν (                    | $0.77 \times V_{IN}$ | V     |

| 3DI N IIIput Level                                        |                   | SDFR = REF (750kHz operation)                            | 1.00                    |                        | 1.35                 | v     |

|                                                           |                   | SDFR = GND (LCD shutdown)                                |                         |                        | 0.5                  |       |

|                                                           |                   | SDFR = IN                                                |                         |                        | +3.0                 |       |

| SDFR Input Current                                        |                   | SDFR = REF                                               | -3.0                    |                        |                      | μΑ    |

|                                                           |                   | SDFR = GND                                               | -3.0                    |                        |                      |       |

### **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 1,  $V_{IN} = 3V$ ,  $V_{SUPB} = 10V$ ,  $\overline{SDFR} = IN$ ,  $C_{REF} = 0.22\mu F$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER                                                 | SYMBOL                | CONDIT                                                             | TIONS                         | MIN   | TYP | MAX   | UNITS   |

|-----------------------------------------------------------|-----------------------|--------------------------------------------------------------------|-------------------------------|-------|-----|-------|---------|

| IN Supply Range                                           | VIN                   |                                                                    |                               | 2.7   |     | 5.5   | V       |

| IN Undervoltage-Lockout                                   |                       | 350mV typical                                                      | V <sub>IN</sub> rising        | 2.5   |     | 2.9   | V       |

| Threshold                                                 | V <sub>UVLO</sub>     | hysteresis                                                         | V <sub>IN</sub> falling       | 2.2   |     | 2.5   | V       |

| IN Quiescent Current                                      | I <sub>IN</sub>       | V <sub>FB</sub> = V <sub>FBP</sub> = V <sub>FBL</sub> = V          | V <sub>FBG</sub> = 1.5V,      |       |     | 1.25  | mA      |

| REF Output Voltage                                        |                       | $-2\mu A < I_{REF} < 100\mu A,$                                    | 2.7V < V <sub>IN</sub> < 5.5V | 1.225 |     | 1.275 | V       |

| MAIN STEP-UP CONTROLLER                                   |                       |                                                                    |                               |       |     |       |         |

| Operation Fragues at                                      | 6                     | SDFR = IN                                                          |                               | 1.275 |     | 1.725 | N 41 1- |

| Operating Frequency                                       | fosc                  | SDFR = REF                                                         |                               | 0.60  |     | 0.90  | MHz     |

| FB Regulation Voltage                                     | $V_{FB}$              | $V_{CS+} - V_{CS-} = 0$                                            |                               | 1.230 |     | 1.270 | V       |

| FB Line Regulation                                        |                       | $V_{IN} = 2.7V \text{ to } 5.5V$                                   |                               |       |     | 0.2   | %/V     |

| FB Input Bias Current                                     |                       | $V_{FB} = 1.5V$                                                    |                               | -100  |     | +100  | nA      |

| CS+ Input Current                                         |                       | $2.2V < V_{CS+} < 6V$                                              |                               |       |     | 90    | μΑ      |

| CS- Input Current                                         |                       | 2.2V < V <sub>CS-</sub> < 6V                                       |                               | -1    |     | +1    | μΑ      |

| Current-Limit Threshold                                   |                       | V <sub>CS+</sub> - V <sub>CS-</sub> , 2.2V < V <sub>CS+</sub> < 6V |                               | 100   |     | 150   | mV      |

| Gate-Drive Output                                         |                       | High or low                                                        |                               |       |     | 5     | Ω       |

| GATE-ON LINEAR-REGULATO                                   | R CONTRO              | LLER (REG P)                                                       |                               |       |     |       |         |

| FBP Regulation Voltage                                    | VFBP                  | $I_{DRVP} = 0.1 mA$                                                |                               | 1.225 |     | 1.275 | V       |

| FBP Input Bias Current                                    |                       | V <sub>FBP</sub> = 1.5V                                            |                               | -250  |     | +250  | nA      |

| FBP Effective Load-Regulation Error (Transconductance)    |                       | V <sub>DRVP</sub> = 10V, I <sub>DRVP</sub> =                       | 0.05mA to 1mA                 |       |     | -2    | %       |

| DRVP Sink Current                                         | I <sub>DRVP</sub>     | $V_{FBP} = 1.1V, V_{DRVP} =$                                       | 10V                           | 2     |     |       | mA      |

| DEL Turn-On Threshold                                     | V <sub>TH</sub> (DEL) |                                                                    |                               | 1.19  |     | 1.31  | V       |

| GAMMA LINEAR-REGULATOR                                    | CONTROL               | ER (REG G, MAX1513                                                 | ONLY)                         |       |     |       |         |

| FBG Regulation Voltage                                    | V <sub>FBG</sub>      | $I_{DRVG} = 0.5mA$                                                 |                               | 1.235 |     | 1.265 | V       |

| FBG to FB Regulation Voltage Matching                     |                       | IDRVG = 0.5mA, V <sub>CS+</sub> - V <sub>CS-</sub> = 0             |                               | -1.2  |     | +1.2  | %       |

| FBG Input Bias Current                                    |                       | V <sub>FBG</sub> = 1.5V                                            |                               | -250  |     | +250  | nA      |

| FBG Effective Load-Regulation<br>Error (Transconductance) |                       | $V_{DRVG} = 10V$ , $I_{DRVG} = 0.25$ mA to 5mA                     |                               |       |     | -2    | %       |

| DRVG Sink Current                                         | IDRVG                 | V <sub>FBG</sub> = 1.1V, V <sub>DRVG</sub> =                       | = 10V                         | 10    |     |       | mA      |

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{IN} = 3V$ ,  $V_{SUPB} = 10V$ ,  $\overline{SDFR} = IN$ ,  $C_{REF} = 0.22\mu F$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER                                                 | SYMBOL            | CONDITIONS                                                   | MIN TY                  | P MAX                | UNITS |

|-----------------------------------------------------------|-------------------|--------------------------------------------------------------|-------------------------|----------------------|-------|

| LOGIC LINEAR-REGULATOR C                                  | ONTROLLE          | R (REG L)                                                    |                         |                      |       |

| FBL Regulation Voltage                                    | V <sub>FBL</sub>  | I <sub>DRVL</sub> = 1mA                                      | 1.225                   | 1.275                | V     |

| FBL Input Bias Current                                    |                   | V <sub>FBL</sub> = 1.5V                                      | -250                    | +250                 | nA    |

| FBL Effective Load-Regulation<br>Error (Transconductance) |                   | V <sub>DRVL</sub> = 3V, I <sub>DRVL</sub> = 0.5mA to 10mA    |                         | -2                   | %     |

| DRVL Sink Current                                         | I <sub>FBL</sub>  | V <sub>FBL</sub> = 1.1V, V <sub>DRVL</sub> = V <sub>IN</sub> | 20                      |                      | mA    |

| GATE-OFF LINEAR-REGULATO                                  | R CONTRO          | DLLER (REG N)                                                |                         |                      |       |

| FBN Regulation Voltage                                    | V <sub>FBN</sub>  | I <sub>DRVN</sub> = 0.2mA                                    | 220                     | 280                  | mV    |

| FBN Input Bias Current                                    |                   | V <sub>FBN</sub> = 0V                                        | -250                    | +250                 | nA    |

| FBN Effective Load-Regulation Error (Transconductance)    |                   | $V_{DRVN} = -10V$ , $I_{DRVN} = 0.1$ mA to 2mA               |                         | 25                   | mV    |

| DRVN Source Current                                       | I <sub>FBN</sub>  | V <sub>FBN</sub> = 0.3V, V <sub>DRVN</sub> = -10V            | 5                       |                      | mA    |

| BUFFER AMPLIFIER                                          |                   |                                                              |                         |                      |       |

| SUPB Supply Range                                         | V <sub>SUPB</sub> |                                                              | 4.5                     | 13.0                 | V     |

| SUPB Supply Current                                       | ISUPB             | No load, V <sub>FBPB</sub> = 4V                              |                         | 1.1                  | mA    |

| FBPB Input Offset Voltage                                 | Vos               | V <sub>FBPB</sub> = V <sub>SUPB</sub> / 2                    |                         | 12                   | mV    |

| FBPB Input Bias Current                                   | IBIAS             | V <sub>FBPB</sub> = V <sub>SUPB</sub> / 2                    |                         | 50                   | nA    |

| FBPB Input Common-Mode<br>Range                           | V <sub>CM</sub>   |                                                              | 0                       | V <sub>SUPB</sub>    | V     |

| Output-Voltage-Swing High                                 | V <sub>OH</sub>   | I <sub>OUTB</sub> = 5mA                                      | V <sub>SUPB</sub> - 150 |                      | mV    |

| Output-Voltage-Swing Low                                  | VoL               | I <sub>OUTB</sub> = -5mA                                     |                         | 150                  | mV    |

| CONTROL INPUTS AND OUTPU                                  | JTS               |                                                              |                         |                      |       |

|                                                           |                   | SDFR = IN (1.5MHz operation)                                 | $0.9 \times V_{IN}$     |                      |       |

| SDFR Input Level                                          |                   | SDFR = unconnected (430kHz operation)                        | $0.69 \times V_{IN}$    | $0.77 \times V_{IN}$ | V     |

| SDFN Input Level                                          |                   | SDFR = REF (750kHz operation)                                | 1.00                    | 1.35                 | V     |

|                                                           |                   | SDFR = GND (LCD shutdown)                                    |                         | 0.5                  |       |

|                                                           |                   | SDFR = IN                                                    |                         | +3.0                 |       |

| SDFR Input Current                                        |                   | SDFR = REF                                                   | -3.0                    |                      | μΑ    |

|                                                           |                   | SDFR = GND                                                   | -3.0                    |                      |       |

Note 1: Specifications to -40°C are guaranteed by design, not production tested.

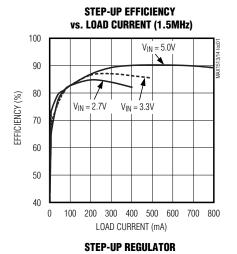

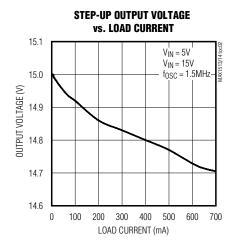

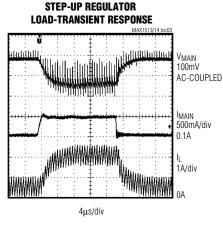

### **Typical Operating Characteristics**

(Circuit of Figure 1, VIN = 5V, VMAIN = 15V, VGON = 25V, VGOFF = -10V, VLOGIC = 3.3V, VGAMMA = 14.7V, TA = +25°C, unless otherwise noted.)

20µs/div

### Typical Operating Characteristics (continued)

(Circuit of Figure 1,  $V_{IN}$  = 5V,  $V_{MAIN}$  = 15V,  $V_{GON}$  = 25V,  $V_{GOFF}$  = -10V,  $V_{LOGIC}$  = 3.3V,  $V_{GAMMA}$  = 14.7V,  $T_A$  = +25°C, unless otherwise noted.)

### Pin Description

| PIN | NA          | ME      | FUNCTION                                                                                                                                                                                                                                                                      |

|-----|-------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN | MAX1513     | MAX1514 | FUNCTION                                                                                                                                                                                                                                                                      |

| 1   | REF         | REF     | Internal Reference. Connect a 0.22µF ceramic capacitor from REF to the analog ground plane, which is connected to GND. External load capability is at least 100µA.                                                                                                            |

| 2   | SDFR SDFR   |         | LCD Shutdown and Frequency-Select Input.  SDFR = GND, LCD shutdown, REF, buffer amplifier and the logic regulator (REG L) output stay on SDFR = IN, 1.5MHz switching frequency  SDRF = REF, 750kHz switching frequency  SDFR = unconnected, 430kHz switching frequency        |

| 3   | FBPB        | N.C.    | Buffer-Amplifier Noninverting Input for the MAX1513. Not internally connected for the MAX1514.                                                                                                                                                                                |

| 4   | OUTB        | N.C.    | Buffer-Amplifier Output for the MAX1513. Not internally connected for the MAX1514.                                                                                                                                                                                            |

| 5   | 5 SUPB N.C. |         | Buffer-Amplifier Supply Input for the MAX1513. Bypass to GND with a $0.1\mu F$ capacitor. Not internally connected for the MAX1514.                                                                                                                                           |

| 6   | FBN         | FBN     | Gate-Off Linear Regulator (REG N) Feedback Input. FBN regulates to 125mV nominal. Connect to the center tap of a resistive voltage-divider between the REG N output and the reference voltage (REF) to set the output voltage. Place the resistive-divider close to this pin. |

| 7   | DEL         | DEL     | Delay-Control Timing Capacitor. Connect a capacitor from DEL to GND to set the gate-on linear-regulator startup delay. See the <i>Power-Up Sequence and Delay Control Block</i> section.                                                                                      |

## \_Pin Description (continued)

|     | NA      | ME                                                                                                                                           |                                                                                                                                                                                                                                                                                                        |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN | MAX1513 | MAX1514                                                                                                                                      | FUNCTION                                                                                                                                                                                                                                                                                               |

| 8   | DRVN    | DRVN                                                                                                                                         | REG N Base Drive. Open drain of an internal P-channel MOSFET. Connect to the base of an external NPN linear-regulator pass transistor.                                                                                                                                                                 |

| 9   | DRVL    | DRVL                                                                                                                                         | Logic Linear-Regulator (REG L) Base Drive. Open drain of an internal N-channel MOSFET. Connect to the base of an external PNP linear-regulator pass transistor.                                                                                                                                        |

| 10  | FBL     | FBL                                                                                                                                          | REG L Feedback Input. FBL regulates to 1.25V (typ). Connect to the center tap of a resistive voltage-divider between the REG L output and the analog ground plane to set the output voltage. Place the resistive voltage-divider close to this pin.                                                    |

| 11  | DRVG    | N.C.                                                                                                                                         | Gamma Linear-Regulator (REG G) Base Drive for the MAX1513. Open drain of an internal N-channel MOSFET. Connect to the base of an external PNP linear-regulator pass transistor. Not internally connected for the MAX1514.                                                                              |

| 12  | FBG     | N.C.                                                                                                                                         | REG G Feedback Input for MAX1513. FBG regulates to 1.25V (typ). Connect to the center tap of a resistive voltage-divider between the REG G output and the analog ground plane to set the output voltage. Place the divider close to the FBG pin. Not internally connected for the MAX1514.             |

| 13  | FBP     | FBP                                                                                                                                          | Gate-On Linear-Regulator (REG P) Feedback Input. FBP regulates to 1.25V (typ). Connect to the center tap of a resistive voltage-divider between the REG P output and the analog ground plane to set the output voltage. Place the resistive-divider close to this pin.                                 |

| 14  | DRVP    | DRVP                                                                                                                                         | REG P Base Drive. Open drain of an internal N-channel MOSFET. Connect to the base of an external PNP linear-regulator pass transistor.                                                                                                                                                                 |

| 15  | GND     | GND                                                                                                                                          | Ground                                                                                                                                                                                                                                                                                                 |

| 16  | GATE    | GATE                                                                                                                                         | External MOSFET Gate Drive. Drives the gate of the step-up switching regulator's MOSFET.                                                                                                                                                                                                               |

| 17  | IN      | IN                                                                                                                                           | Supply Input. IN powers all the internal circuitry of the MAX1513/MAX1514. The input voltage range is from 2.7V to 5.5V. Bypass with a 0.1µF ceramic capacitor between IN and GND. Place the capacitor within 5mm of IN.                                                                               |

| 18  | CS+     | CS+ Current-Sense-Comparator Noninverting Input. Connect CS+ and CS- to the lossless currer network. See the Lossless Current Sense section. |                                                                                                                                                                                                                                                                                                        |

| 19  | CS-     | CS-                                                                                                                                          | Current-Sense-Comparator Inverting Input. Connect CS+ and CS- to the lossless current-sense network. See the <i>Lossless Current Sense</i> section.                                                                                                                                                    |

| 20  | FB      | FB                                                                                                                                           | Main Step-Up Regulator Feedback Input. FB regulates to 1.25V (typ). Connect to the center tap of a resistive voltage-divider between the main output (V <sub>MAIN</sub> ) and the analog ground plane to set the main step-up regulator output voltage. Place the resistive-divider close to this pin. |

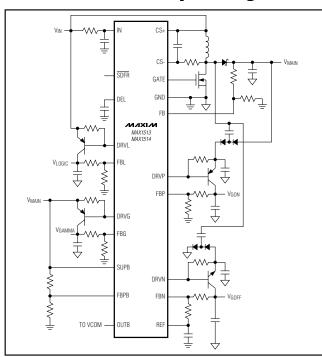

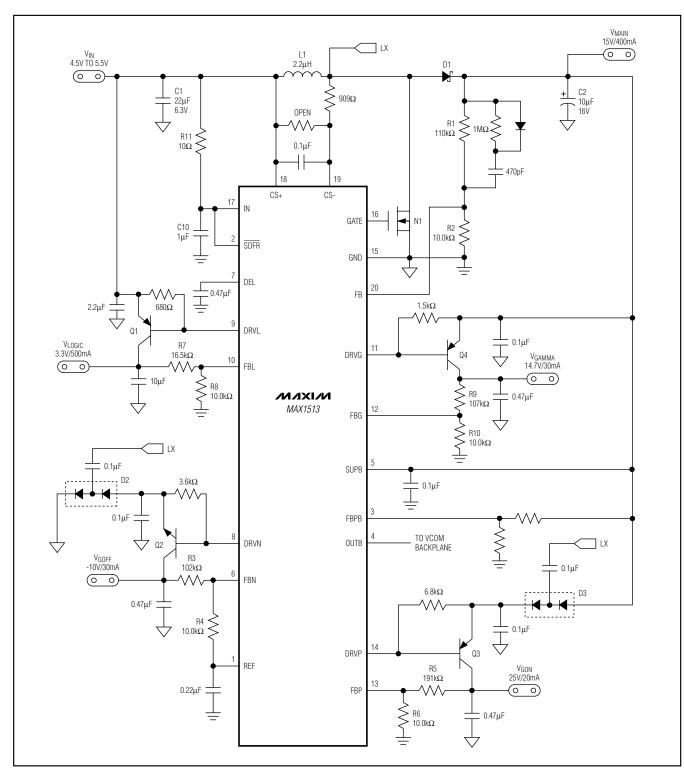

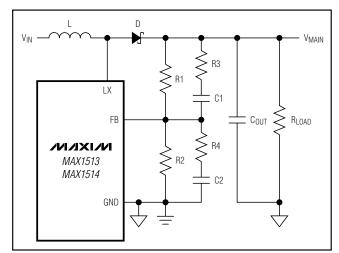

Figure 1. Typical Operating Circuit of the MAX1513

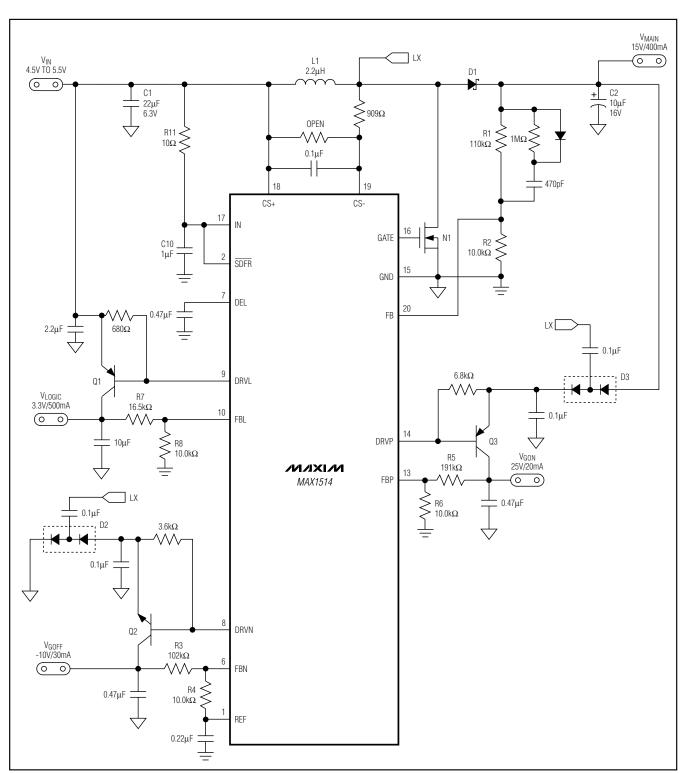

Figure 2. Typical Operating Circuit of the MAX1514

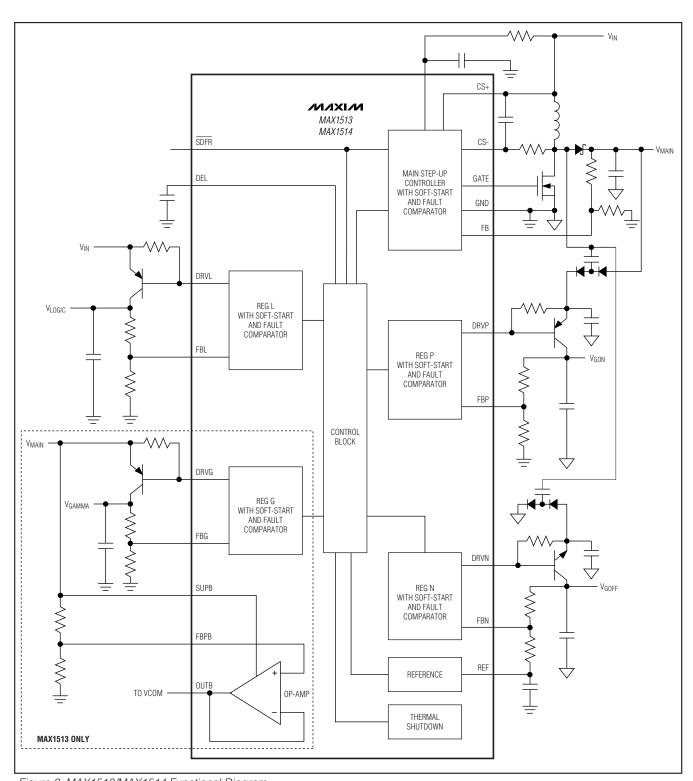

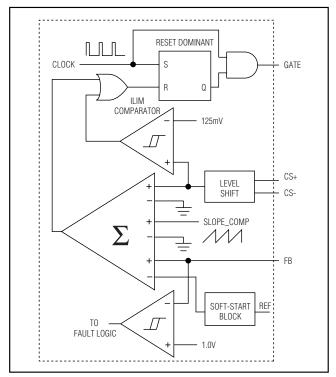

Figure 3. MAX1513/MAX1514 Functional Diagram

12 \_\_\_\_\_\_\_**/\/\/\**

### Typical Operating Circuit

The typical operating circuit of the MAX1513 (Figure 1) is a complete power-supply system for TFT LCDs. The circuit generates a +15V source-driver supply, +25V and -10V gate-driver supplies, a +3.3V logic supply for the timing controller, a 14.7V gamma-correction string supply and a VCOM buffer. The typical operating circuit of the MAX1514 (Figure 2) is similar to that of the MAX1513 except the gamma-correction string supply and the VCOM buffer have been eliminated. The input voltage range for the IC is from +2.7V to +5.5V. The typical operating circuits' listed load currents are available from a +4.5V to +5.5V supply. Table 1 lists recommended component options, and Table 2 lists the component suppliers' contact information.

**Table 1. Component List**

| DESIGNATION | DESCRIPTION                                                               |

|-------------|---------------------------------------------------------------------------|

| C1          | 22µF ±20%, 6.3V X5R ceramic capacitor (1206)<br>Taiyo Yuden JMK316BJ226ML |

| C2          | 10µF ±20%, 16V POSCAP (D10)<br>Sanyo 16AQU10M                             |

| D1          | 1A, 30V Schottky diode (S-Flat)<br>Toshiba CRS02                          |

| D2, D3      | 200mA, 100V diodes (SOT23)<br>Fairchild MMBT4148SE                        |

| L1          | 2.2µH, 3.3A inductor<br>Sumida CLS7D16NP-2R2NC                            |

| N1          | 3A, 20V N-channel MOSFET (SOT23)<br>Fairchild FDN339AN                    |

| Q1          | 3A, 60V PNP bipolar transistor (SOT23)<br>Fairchild NZT660                |

| Q2          | 200mA, 40V NPN bipolar transistor (SOT23)<br>Fairchild MMBT3904           |

| Q3, Q4      | 200mA, 40V PNP bipolar transistors (SOT23)<br>Fairchild MMBT3906          |

### \_Detailed Description

The MAX1513 and MAX1514 contain a high-performance, step-up switching-regulator controller and three linear-regulator controllers (two positive and one negative). The MAX1513 also includes an additional linear-regulator controller and a high-current buffer amplifier. Figure 3 shows the MAX1513/MAX1514 functional diagram.

### Main Step-Up Regulator Controller

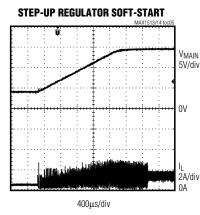

The main step-up regulator controller drives an external N-channel power MOSFET to generate the TFT-LCD source-driver supply. The controller employs a current-mode, fixed-frequency PWM architecture to maximize loop bandwidth and provide fast transient response to pulsed loads found in source-driver applications. The multilevel control input \$\overline{SDFR}\$ sets the switching frequency to 430kHz, 750kHz, or 1.5MHz. The high switching frequency allows the use of low-profile inductors and ceramic capacitors to minimize the thickness of LCD panel designs, while maintaining high efficiency using a lossless current-sense method. The IC's built-in soft-start function reduces the inrush current during startup.

The controller regulates the output voltage and the power delivered to the output by modulating the duty cycle (D) of the power MOSFET in each switching cycle. The duty cycle of the MOSFET is approximated by:

$$D \approx \frac{V_{MAIN} - V_{IN}}{V_{MAIN}}$$

Figure 4 shows the functional diagram of the step-up regulator controller. The core of the controller is a multi-input summing comparator that sums three signals: the output-voltage error signal with respect to the reference voltage, the current-sense signal, and the slope-compensation ramp. On the rising edge of the internal clock, the controller sets a flip-flop, which turns on the external N-channel MOSFET, applying the input voltage across the inductor. The current through the inductor ramps up linearly, storing energy in its magnetic field. Once the sum of the feedback voltage error, slope compensation, and current-sense signals trip the multi-

**Table 2. Component Suppliers**

| SUPPLIER                | PHONE        | FAX          | WEBSITE               |

|-------------------------|--------------|--------------|-----------------------|

| Fairchild Semiconductor | 408-822-2000 | 408-822-2102 | www.fairchildsemi.com |

| Sumida                  | 847-545-6700 | 847-545-6720 | www.sumida.com        |

| Taiyo Yuden             | 800-348-2496 | 847-925-0899 | www.t-yuden.com       |

| TDK                     | 847-803-6100 | 847-390-4405 | www.component.tdk.com |

| Toshiba                 | 949-455-2000 | 949-859-3963 | www.toshiba.com       |

input PWM comparator, the flip-flop is reset and the MOSFET turns off. Since the inductor current is continuous, a transverse potential develops across the inductor that turns on the diode (D1). The voltage across the inductor then becomes the difference between the output voltage and the input voltage. This discharge condition forces the current through the inductor to ramp down, transferring the energy stored in the magnetic field to the output capacitor and the load. The N-channel MOSFET is kept off for the rest of the clock cycle.

# Current Limiting and Current-Sense Amplifier (CS+, CS-)

The internal current-limit circuit resets the PWM flip-flop and turns off the external power MOSFET whenever the voltage difference between CS+ and CS- exceeds 125mV (typ). The tolerance on this current limit is ±20%. Use the minimum value of the current limit to select components of the current-sense network.

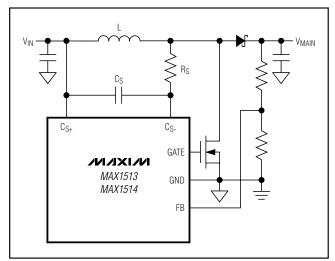

#### Lossless Current Sense

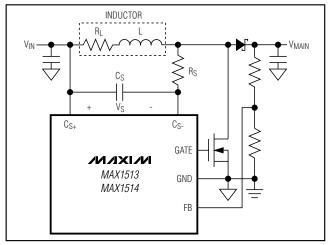

The lossless current-sense method uses the DC resistance (DCR) of the inductor as the sense element. Figure 5 shows a simplified step-up regulator using the basic lossless current-sensing method. An RC network is connected in parallel with the step-up inductor (L). The voltage across the sense capacitor (Cs) is the

Figure 4. Step-Up Regulator-Controller Functional Diagram

input to the current-sense amplifier. To prevent the sense amplifier from seeing large common-mode switching voltages, the sense capacitor should always be connected to the nonswitching end of the inductor (i.e., the input of the step-up regulator).

Lossless current sense can be easily understood using complex frequency domain analysis. The voltage across the inductor is given by:

$$V_L = I_L(sL + R_L)$$

where L is the inductance,  $R_L$  is the DCR of the inductor, and  $I_L$  is the inductor current. The voltage across the sense capacitor is given by:

$$V_{S} = \frac{1}{1 + sR_{S}C_{S}}V_{L}$$

where Rs is the series resistor in the sense network and Cs is the sense capacitor. The above equation can be rewritten as:

$$V_S = \frac{sL + R_L}{1 + sR_SC_S}I_L = \frac{1 + sL/R_L}{1 + sR_SC_S}R_LI_L$$

If  $\frac{L}{R_I} = R_S C_S$ , then the equation becomes:

$$V_S = R_I I_I$$

Therefore, the sense capacitor voltage is directly proportional to the inductor current if the time constant of the RC sense network matches the time constant of the inductor/DCR. The sense method is equivalent to using a current-sense resistor that has the same value as the inductor DCR.

Figure 5. Step-Up Regulator Using Lossless Current Sensing

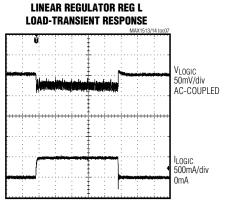

#### Logic Linear-Regulator Controller

The logic linear-regulator controller (REG L) is an analog gain block with an open-drain N-channel output. It drives an external PNP pass transistor with a  $680\Omega$  base-to-emitter resistor (Figure 1). Its guaranteed base-drive sink current is at least 10mA. The regulator, including transistor Q1 in Figure 1, uses a  $10\mu\text{F}$  ceramic output capacitor and is designed to deliver 500mA at 3.3V. Other output voltages and currents are possible by scaling the pass transistor, input capacitor, and output capacitor. See the *Pass-Transistor Selection* and *Stability Requirements* sections.

REG L is typically used to generate low-voltage logic supplies for the timing controller and the digital sections of the TFT-LCD source/gate-drive ICs.

REG L is automatically enabled when the input voltage is above the UVLO threshold. Each time it is enabled, the controller goes through a soft-start routine that ramps up its internal reference DAC in 128 steps.

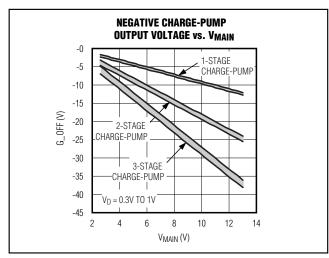

### Gate-Off Linear-Regulator Controller

The gate-off linear-regulator controller (REG N) is an analog gain block with an open-drain P-channel output. It drives an external NPN pass transistor with a  $3.6 \mathrm{k}\Omega$  base-to-emitter resistor (Figure 1). Its guaranteed base-drive source current is at least 2mA. The regulator, including Q2 in Figure 1, uses a  $0.47 \mu \mathrm{F}$  ceramic output capacitor and is designed to deliver 30mA at -10V. Other output voltages and currents are possible by scaling the pass transistor, input capacitor, and output capacitor. See the <code>Pass-Transistor Selection</code> and <code>Stability Requirements</code> sections.

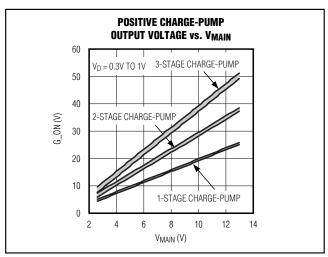

REG N is typically used to provide the TFT-LCD gate drivers' gate-off voltage. A negative voltage can be produced using a charge-pump circuit as shown in Figure 1.

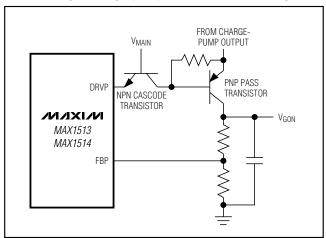

Figure 6. Using an NPN Cascode for Charge-Pump Output Voltages > 28V

REG N is enabled after the logic linear-regulator REG L soft-start has completed. Each time it is enabled, the control goes through a soft-start routine that ramps down its internal reference DAC from  $V_{\text{REF}}$  to 250mV in about 100 steps.

### **Gate-On Linear-Regulator Controller**

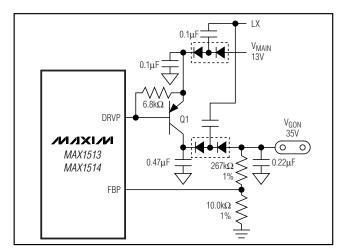

The gate-on linear-regulator controller (REG P) is an analog gain block with an open-drain N-channel output. It drives an external PNP pass transistor with a  $6.8k\Omega$  base-to-emitter resistor (Figure 1). Its guaranteed base-drive sink current is at least 1mA. The regulator including Q3 in Figure 1 uses a  $0.47\mu\text{F}$  ceramic output capacitor and is designed to deliver 20mA at 25V. Other output voltages and currents are possible by scaling the pass transistor, input capacitor, and output capacitor. See the *Pass-Transistor Selection* and *Stability Requirements* sections.

REG P is typically used to provide the TFT-LCD gate drivers' gate-on voltage. Use a charge pump with as many stages as necessary to obtain a voltage exceeding the required gate-on voltage (see the *Selecting the Number of Charge-Pump Stages* section). Note that the voltage rating of the DRVP output is 28V. If the charge-pump output voltage can exceed 28V, an external cascode-connected NPN transistor should be added (Figure 6). Alternately, the linear regulator can control an intermediate charge-pump state while regulating the final charge-pump output (Figure 7).

REG P is enabled after the step-up regulator soft-start has completed and the voltage on DEL exceeds 1.25V. Each time it is enabled, the controller goes through a soft-start routine that ramps up its internal reference DAC in 128 steps.

Figure 7. Linear Regulator Controls Intermediate Charge-Pump Stage

# Gamma Linear-Regulator Controller (MAX1513 Only)

The gamma linear-regulator controller REG G is an analog gain block with an open-drain N-channel output. It drives an external PNP pass transistor with a  $1.5 \mathrm{k}\Omega$  base-to-emitter resistor (Figure 1). Its guaranteed base-drive sink current is at least 5mA. The regulator, including Q4 in Figure 1, uses a  $0.47 \mu \mathrm{F}$  ceramic output capacitor, and the controller is designed to deliver 40mA at 14.7V. Other output voltages and currents are possible by scaling the pass transistor, input capacitor, and output capacitor. See the <code>Pass-Transistor Selection</code> and <code>Stability Requirements</code> sections.

REG G is typically used to provide the TFT-LCD gamma reference voltage, which is usually 0.3V below the source-drive supply voltage.

REG G is enabled 2.7ms after REG P's soft-start has completed. Each time it is enabled, the controller goes through a soft-start routine that ramps up its internal reference DAC in 128 steps.

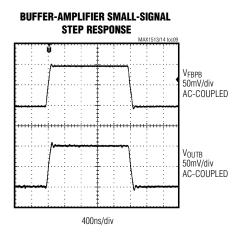

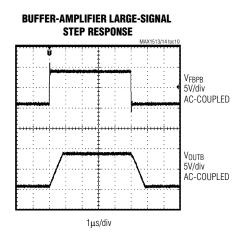

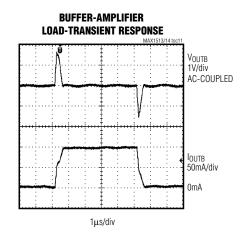

### **Buffer Amplifier (MAX1513 Only)**

The MAX1513 includes a buffer amplifier that is typically used to drive the LCD backplane (VCOM) or the gamma-correction divider string. The buffer amplifier features ±150mA output short-circuit current, 10V/µs slew rate, and 12MHz bandwidth. The Rail-to-Rail® input and output capability maximizes its flexibility.

#### Short-Circuit Current Limit

The MAX1513's buffer amplifier limits short-circuit current to approximately  $\pm 150$ mA if the output is directly shorted to SUPB or to GND. If the short-circuit condition persists, the junction temperature of the IC rises until it reaches the thermal-shutdown threshold ( $\pm 160^{\circ}$ C typ). Once the junction temperature reaches the thermal-shutdown threshold, an internal thermal sensor immediately sets the thermal fault latch, shutting off all the IC's outputs. The device remains inactive until the input voltage is cycled below VUVLO.

#### **Driving Pure Capacitive Load**

The buffer amplifier is typically used to drive the LCD backplane (VCOM) or the gamma-correction divider string. The LCD backplane consists of a distributed series capacitance and resistance, a load that can be easily driven by the buffer amplifier. When driving a pure capacitive load, the amplifier's gain peaking increases. A  $5\Omega$  to  $50\Omega$  resistor placed between OUTB and the capacitive load reduces peaking.

### **Undervoltage Lockout**

The undervoltage-lockout (UVLO) circuit compares the voltage at the IN pin with the UVLO threshold (2.7V ris-

ing, 2.35V falling, typ) to ensure the input voltage is high enough for reliable operation. The 350mV (typ) hysteresis prevents supply transients from causing a restart. Once the input voltage exceeds the UVLO rising threshold, the IC is allowed to start. When the input voltage falls below the UVLO falling threshold, all the regulator outputs (including REF) are disabled until the input voltage exceeds the UVLO rising threshold.

### Reference Voltage (REF)

The reference output is nominally 1.25V and can source at least 100µA without degrading its accuracy (see the *Typical Operating Characteristics*). Bypass REF with a 0.22µF ceramic capacitor connected between REF and the analog ground plane (which connects to GND).

### Shutdown and Oscillator-Frequency Selection

The four-level logic input \$\overline{SDFR}\$ controls shutdown and oscillator-frequency selection. Connecting \$\overline{SDFR}\$ to ground shuts off all the regulator outputs except the logic linear-regulator controller (REG L), buffer amplifier, and REF. Connecting \$\overline{SDFR}\$ to \$\overline{IN}\$ sets the oscillator frequency to 1.5MHz. Connecting \$\overline{SDFR}\$ to \$\overline{REF}\$ sets the oscillator frequency to 750kHz. Leaving \$\overline{SDFR}\$ unconnected sets the oscillator frequency to 430kHz. When \$\overline{SDFR}\$ is left unconnected, bypass the pin to ground with a 1000pF to 0.1µF capacitor to prevent switching noise from coupling into the pin's high input impedance. Note the soft-start period and the fault-timer period do not change with the oscillator frequency.

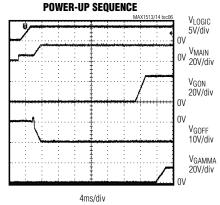

### Power-Up Sequence and Delay Control Block

Once the voltage on IN exceeds the UVLO rising threshold (2.7V typ), the internal reference is enabled. With a 0.22µF REF bypass capacitor, the reference reaches its regulation voltage of 1.25V in approximately 1ms. When the reference voltage is ready, the MAX1513/MAX1514 enable the logic linear regulator. The MAX1513 also enables the buffer amplifier at the same time. Once the logic linear-regulator soft-start is completed, the MAX1513/MAX1514 enable the step-up regulator and REG N simultaneously. Once the soft-start of the step-up regulator is completed, the MAX1513/MAX1514 enable the delay control block. An internal 5µA current starts charging the timing capacitor on DEL. When the voltage on DEL reaches 1.25V, the MAX1513/MAX1514 enable REG P. With a 0.1µF capacitor on DEL, the DEL voltage reaches 1.25V in about 25ms. The MAX1513 enables the gamma linear regulator 2.7ms after the soft-start of REG P is completed.

Rail-to-Rail is a registered trademark of Nippon Motorola, Ltd.

#### Soft-Start

Each positive regulator (step-up regulator, REG P, REG L, and REG G) includes a 7-bit soft-start DAC whose input is the reference, and whose output is stepped in 128 steps from zero up to the reference voltage. The soft-start DAC of the negative regulator (REG N) steps from the reference down to 250mV in about 100 steps. The outputs of the soft-start DACs determine the set points of each regulator. The soft-start duration is 2.7ms (typ) for each positive regulator and about 2.2ms for the negative regulator. The soft-start is independent of the selected operating frequency.

#### **Fault Protection**

During steady-state operation, if the step-up regulator output or any of the linear-regulator outputs does not exceed its respective fault detection threshold, the MAX1513/MAX1514 activate an internal fault timer. If any condition or the combination of conditions indicates a continuous fault for the fault-timer duration (43.6ms typ), the MAX1513/MAX1514 set the fault latch, shutting down all the outputs except the reference. Once the fault condition is removed, toggle SDFR (below 0.4V) or cycle the input voltage (below 2.2V) to clear the fault latch and reactivate the device. The fault-detection circuit is disabled during the soft-start time of each regulator.

#### Thermal-Overload Protection

The thermal-overload protection prevents excessive power dissipation from overheating the MAX1513/MAX1514. When the junction temperature exceeds +160°C, a thermal sensor immediately activates the fault-protection circuit, which shuts down all the outputs except the reference, allowing the device to cool down. Once the device cools down by approximately 15°C, cycle the input voltage (below the UVLO falling threshold) to clear the fault latch and reactivate the device.

The thermal-overload protection protects the controller in the event of fault conditions. For continuous operation, do not exceed the absolute maximum junction temperature rating of  $T_J = +150$ °C.

### Design Procedure

### Main Step-Up Regulator

#### Inductor Selection

The minimum inductance value, peak current rating, and DC series resistance (DCR) are factors to consider when selecting the inductor. These factors influence the converter's efficiency, maximum output load capability, transient-response time, and output voltage ripple. Size and cost are also important factors to consider.

The maximum output current, input voltage, output voltage, and switching frequency determine the inductor value. Very high inductance values minimize the current ripple and therefore reduce the peak current, which decreases core losses in the inductor and I<sup>2</sup>R losses in the entire power path. However, large inductor values also require more energy storage and more turns of wire, which increases size and can increase I<sup>2</sup>R losses in the inductor. Low inductance values decrease the size but increase the current ripple and peak current. Finding the best inductor involves choosing the best compromise between circuit efficiency, inductor size, and cost.

The equations used here include a constant, LIR, which is the ratio of the inductor peak-to-peak ripple current to the average DC inductor current at the full load current. The best trade-off between inductor size and circuit efficiency for step-up regulators generally has an LIR between 0.3 and 0.5. However, depending on the AC characteristics of the inductor core material and the ratio of inductor resistance to other power-path resistances, the best LIR can shift up or down. If the inductor resistance is relatively high, more ripple can be accepted to reduce the number of turns required and increase the wire diameter. If the inductor resistance is relatively low, increasing inductance to lower the peak current can decrease losses throughout the power path. If extremely thin high-resistance inductors are used, as is common for LCD panel applications, the best LIR can increase to between 0.5 and 1.0.

Once an inductor is chosen, higher and lower values for the inductor should be evaluated for efficiency improvements in typical operating regions.

Determine the inductor value and peak current requirement as follows:

Since the current delivered by charge pumps connected to LX adds to the inductor current, calculate the effective maximum output current, IMAIN(EFF):

$$I_{MAIN(EFF)} = I_{MAIN(MAX)} + n_{NEG} \times I_{NEG} + (n_{POS} + 1) \times I_{POS}$$

where  $I_{MAIN(MAX)}$  is the maximum output current including any gamma-regulator current,  $n_{NEG}$  is the number of negative charge-pump stages,  $n_{NEG}$  is the number of positive charge-pump stages,  $I_{NEG}$  is the negative charge-pump output current, and  $I_{POS}$  is the positive charge-pump output current, assuming the pump source for  $I_{POS}$  is  $V_{MAIN}$ .

Calculate the approximate inductor value using the typical input voltage ( $V_{IN}$ ), the expected efficiency ( $\eta_{TYP}$ )

taken from an appropriate curve in the *Typical Operating Characteristics*, and an estimate of LIR based on the above paragraphs:

$$L = \left(\frac{V_{IN}}{V_{MAIN}}\right)^{2} \left(\frac{V_{MAIN} - V_{IN}}{I_{MAIN(EFF)} \times f_{OSC}}\right) \left(\frac{\eta_{TYP}}{LIR}\right)$$

Choose an available inductor value from an appropriate inductor family. Calculate the maximum DC input current at the minimum input voltage (VIN(MIN)) using the following equation:

$$I_{IN(DC,\;MAX)} \; = \; \frac{I_{IMAIN(EFF)} \, \times \, V_{MAIN}}{V_{IN(MIN)} \times \, \eta_{MIN}} \label{eq:Inverse_INV}$$

The expected efficiency at that operating point  $(\eta_{MIN})$  can be taken from an appropriate curve in the *Typical Operating Characteristics*.

Calculate the ripple current at that operating point and the peak current required for the inductor:

$$\begin{split} I_{\text{RIPPLE}} \; &= \; \frac{V_{\text{IN(MIN)}} \, \times \left( V_{\text{MAIN}} \, - \, V_{\text{IN(MIN)}} \right)}{L \, \times \, V_{\text{MAIN}} \, \times \, f_{\text{OSC}}} \\ I_{\text{PEAK}} \; &= \; I_{\text{IN(DC, MAX)}} + \, \frac{I_{\text{RIPPLE}}}{2} \end{split}$$

The inductor's saturation current rating and the MAX1513/MAX1514s' current limit (I<sub>LIM</sub>) should exceed I<sub>PEAK</sub>, and the inductor's DC current rating should exceed I<sub>IN(DC, MAX)</sub>.

Considering the typical operating circuit, the maximum load current (I<sub>MAIN(MAX)</sub>) is 400mA for I<sub>MAIN</sub> directly and 30mA for REG G to provide V<sub>GAMMA</sub>. The one-stage negative charge pump provides 30mA to REG N for V<sub>GOFF</sub>, and the one-stage positive charge pump provides 20mA to REG P for V<sub>GON</sub>. Altogether, the effective maximum output current (I<sub>MAIN(EFF)</sub>) is 500mA with a 15V output and a typical 5V input voltage. The switching frequency is set to 1.5MHz. Choosing an LIR of 0.6 and estimating efficiency of 85% at this operating point:

$$L = \left(\frac{5V}{15V}\right)^{2} \left(\frac{15V - 5V}{0.5A \times 1.5MHz}\right) \left(\frac{0.85}{0.6}\right) \approx 2.2\mu H$$

Using the circuit's minimum input voltage (4.5V) and estimating efficiency of 80% at that operating point:

$$I_{\text{IN(DC, MAX)}} = \frac{0.5A \times 15V}{4.5V \times 0.8} \approx 2.1A$$

The ripple current and the peak current are:

$$I_{RIPPLE} = \frac{4.5V \times (15V - 4.5V)}{2.2\mu H \times 15V \times 1.5MHz} \approx 1.0A$$

$I_{PEAK} = 2.1A + \frac{1.0A}{2} \approx 2.6A$

The inductor DCR should be low enough for reasonable efficiency. As a rule of thumb, do not allow the voltage drop across the inductor DCR to exceed a few percent of the input voltage at IPEAK.

Many notebook panel designs have height constraints on the components. If a thin inductor with the required current rating is not available, use two thin inductors in series or parallel.

#### **Current-Sense Network Selection**

After selecting the inductor, use the following steps to design the current-sense network for lossless current sensing.

1) Calculate the RC time constant of the sense network using the typical inductance and typical DCR:

$$\tau = \frac{L}{R_{L(TYP)}}$$

2) Determine the component values of the sense network. Select Cs, and then calculate Rs using:

$$R_S = \frac{\tau}{C_S}$$

3) Calculate the worst-case high sense voltage over temperature using the maximum DCR value (R<sub>L(MAX)</sub>) found in the inductor technical specifications:

$$V_{SENSE} = I_{PEAK} \times R_{L(MAX)} \times (1 + TC \times \Delta T)$$

where IPEAK is the peak inductor current calculated in the *Inductor Selection* section, TC is the temperature coefficient of copper (0.5%/°C) and  $\Delta T$  is the difference between the specified temperature for R<sub>L(MAX)</sub> and the maximum expected inductor temperature.

4) Compare the calculated sense voltage with the minimum value of the current-limit threshold in the *Electrical Characteristics* (100mV). If the sense voltage is between 80mV and 100mV, use the current-sense configuration in Figure 8 with the calculated C<sub>S</sub> and R<sub>S</sub> above.

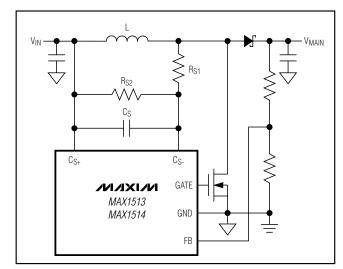

5) If VSENSE is greater than 100mV, the current-feed-back signal is too high and can trip the current limit before the full load current is delivered. Use the current-sense configuration in Figure 9 to attenuate the sense signal. Define the scale factor (SF) as:

$$SF = \frac{100mV}{V_{SENSE}}$$

Calculate Rs1 and Rs2:

$$R_{S1} = \frac{R_S}{SF}$$

$$R_{S2} = \frac{R_{S1} \times SF}{1 - SF}$$

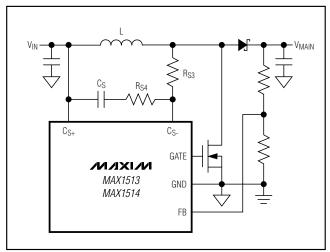

6) If VSENSE is less than 80mV, the current-feedback signal is low relative to the current-limit threshold. Use the Figure 8 configuration, or, if good current-limit accuracy is desired, use the optional current-sense configuration in Figure 10 to increase the amplitude of the sense signal. Calculate Rs3 and Rs4:

$$\begin{split} R_{S3} &= \frac{V_{MAIN} - V_{IN(MIN)}}{V_{MAIN} - V_{IN(MIN)} - 100 mV + V_{SENSE}} \times \ R_{S} \\ R_{S4} &= R_{S} - R_{S3} \end{split}$$

If the 2.2µH inductor used in the typical operating circuit (Figures 1 and 2) had a typical DCR of  $24m\Omega$  and a maximum DCR of  $30m\Omega$ , the RC time constant of the sense network would be:

Figure 8. Lossless Current Sensing with 80mV < VSENSE < 100mV

$$\tau = \frac{2.2\mu H}{24m\Omega} = 91.7\mu s$$

Select Cs = 0.1µF and calculate Rs:

$$R_S = \frac{91.7\mu s}{0.1\mu F} = 917\Omega$$

Assuming  $\Delta T$  is 40°C and TC is 0.5%, the worst-case high sense voltage over temperature is:

$$V_{SENSE} = 2.6A \times 30m\Omega (1 + 0.005 \times 40^{\circ}C) = 93.6mV$$

Because V<sub>SENSE</sub> would be between 80mV and 100mV, the circuit in Figure 8 should be used. The closest 1% standard value for Rs is  $909\Omega$ .

If the 2.2µH inductor used in the typical operating circuit (Figures 1 and 2) has a typical DCR of  $45m\Omega$  and a maximum DCR of  $56m\Omega$ , the RC time constant of the sense network is:

$$\tau = \frac{2.2 \mu H}{45 m \Omega} = 48.9 \mu s$$

Select  $C_S = 0.1 \mu F$  and calculate  $R_S$ :

$$R_S = \frac{48.9 \mu s}{0.1 \mu F} = 489 \Omega$$

Assuming  $\Delta T$  is 40°C and TC is 0.5%, the worst-case high sense voltage over temperature is:

Figure 9. Lossless Current Sensing with VSENSE > 100mV

Figure 10. Lossless Current Sensing with VSENSE < 80mV

$$V_{SENSE} = 2.6A \times 56m\Omega (1 + 0.005 \times 40^{\circ}C) = 175mV$$

Because VSENSE would be greater than 100mV, the circuit in Figure 9 should be used and the scale factor is:

$$SF = \frac{100mV}{175mV} = 0.571$$

Calculate Rs1 and Rs2:

$$R_{S1} = \frac{489\Omega}{0.571} = 856\Omega$$

$$R_{S2} = \frac{856 \times 0.571}{1 - 0.571} = 1139\Omega$$

The closest 1% standard values for Rs1 and Rs2 are  $866\Omega$  and  $1.13k\Omega,$  respectively.

If the 2.2µH inductor used in the typical operating circuit (Figures 1 and 2) has a typical DCR of  $10m\Omega$  and a maximum DCR of  $14m\Omega$ , the RC time constant of the sense network is:

$$\tau = \frac{2.2\mu H}{10m\Omega} = 220\mu s$$

Select  $C_S = 0.1 \mu F$ ,  $R_S$  is:

$$R_S = \frac{220 \mu s}{0.1 \mu F} = 2200 \Omega$$