## EMIF10-1K010F2

IPAD™

## EMI FILTER INCLUDING ESD PROTECTION

## MAIN PRODUCT CHARACTERISTICS:

Where EMI filtering in ESD sensitive equipment is required

- Mobile phones and communication systems

- Computers, printers and MCU Boards

## DESCRIPTION

The EMIF10-1K010F2 is a highly integrated devices designed to suppress EMI/RFI noise in all systems subjected to electromagnetic interferences. The EMIF10 flip chip packaging means the package size is equal to the die size. This filter includes an ESD protection circuitry which prevents the device from destruction when subjected to ESD surges up 15kV.

## BENEFITS

- EMI symmetrical (I/O) low-pass filter

- High efficiency in EMI filtering

- Lead free package

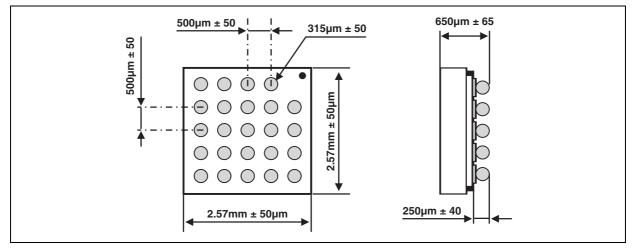

- Very low PCB space consuming: 2.57 mm x 2.57 mm

- Very thin package: 0.65 mm

- High efficiency in ESD suppression

- High reliability offered by monolithic integration

- High reducing of parasitic elements through integration & wafer level packaging.

## COMPLIES WITH THE FOLLOWING STANDARDS: IEC61000-4-2

Level 4 15kV (air discharge) 8kV (contact discharge)

### MIL STD 883E -Method 3015-6 Class 3

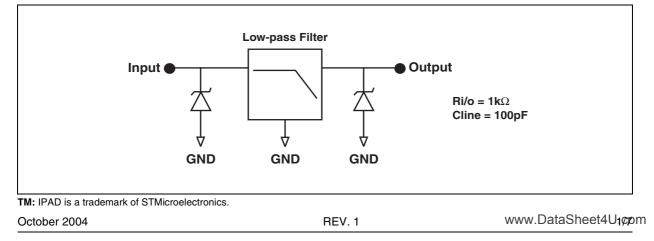

#### Figure 2: Basic Cell Configuration

#### Table 1: Order Code

| Part Number    | Marking |  |

|----------------|---------|--|

| EMIF10-1K010F2 | FD      |  |

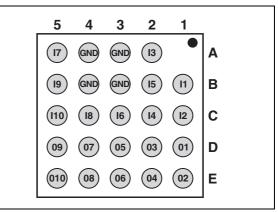

## Figure 1: Pin Configuration (ball side)

## EMIF10-1K010F2

| Symbol           | Parameter and test conditions | Value         | Unit |

|------------------|-------------------------------|---------------|------|

| Tj               | Junction temperature          | 125           | °C   |

| T <sub>op</sub>  | Operating temperature range   | - 40 to + 85  | °C   |

| T <sub>stg</sub> | Storage temperature range     | - 55 to + 150 | °C   |

## Table 2: Absolute Maximum Ratings (T<sub>amb</sub> = 25°C)

## Table 3: Electrical Characteristics ( $T_{amb} = 25^{\circ}C$ )

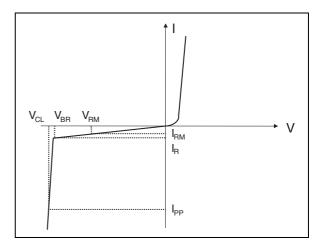

| Symbol           | Parameters                               |  |

|------------------|------------------------------------------|--|

| V <sub>BR</sub>  | Breakdown voltage                        |  |

| I <sub>RM</sub>  | Leakage current @ V <sub>RM</sub>        |  |

| V <sub>RM</sub>  | Stand-off voltage                        |  |

| V <sub>CL</sub>  | Clamping voltage                         |  |

| R <sub>d</sub>   | Dynamic impedance                        |  |

| I <sub>PP</sub>  | Peak pulse current                       |  |

| R <sub>I/O</sub> | Series resistance between Input & Output |  |

| C <sub>in</sub>  | Input capacitance per line               |  |

| Symbol            | Test conditions               | Min. | Тур. | Max. | Unit |

|-------------------|-------------------------------|------|------|------|------|

| V <sub>BR</sub>   | I <sub>R</sub> = 1 mA         | 6    | 8    | 10   | V    |

| I <sub>RM</sub>   | V <sub>RM</sub> = 3V per line |      |      | 500  | nA   |

| R <sub>I/O</sub>  |                               | 900  | 1000 | 1100 | Ω    |

| R <sub>line</sub> | At 0V bias                    | 80   | 100  | 120  | pF   |

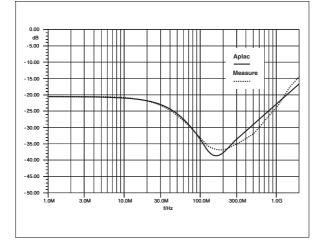

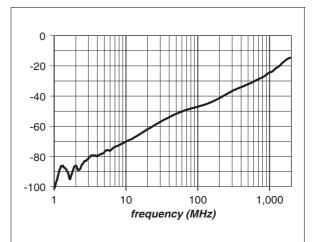

# Figure 3: S21 (dB) attenuation measurement and Aplac simulation

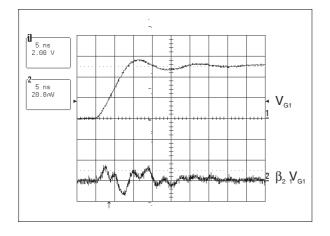

## Figure 4: Analog crosstalk measurements

## Figure 5: Digital crosstalk measurement

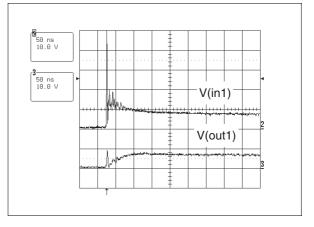

Figure 7: ESD response to IEC61000-4-2 (-15kV air discharge) on one input V(in) and on one output (Vout)

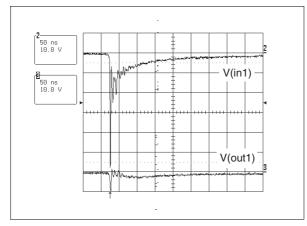

Figure 6: ESD response to IEC61000-4-2 (+15kV air disc.harge) on one input V(in) and on one output (Vout)

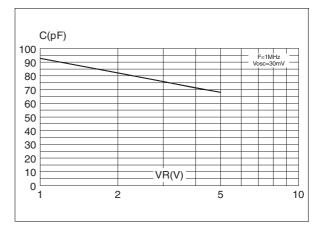

Figure 8: Line capacitance versus applied voltage

## EMIF10-1K010F2

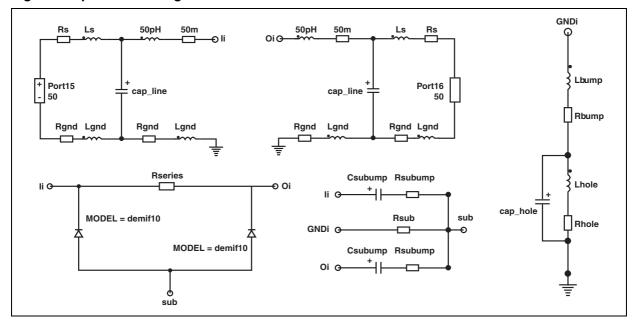

Figure 9: Aplac model single line structure

## Figure 10: Aplac model parameters

| Cz       | 57pF      | Model demif10 |  |

|----------|-----------|---------------|--|

| Rseries  | 960       | BV = 7        |  |

| cap_line | 0.8pF     | IBV = 1m      |  |

| Ls       | 0.6nH     | CJO = Cz      |  |

| Rbump    | 50m       | M = 0.3333    |  |

| Lbump    | 50pH      | Rs = 1        |  |

| Rs       | 0.15      | VJ = 0.6      |  |

| Csubump  | 15pF      | TT = 100n     |  |

| Rsubump  | 0.15      |               |  |

| Rsub     | 0.1       |               |  |

| lhole    | 1.2nH opt |               |  |

| Rhole    | 0.15      |               |  |

| cap_hole | 0.15pF    |               |  |

| Rgnd     | 0.25      |               |  |

| Ignd     | 0.4nH     |               |  |

| 5        |           |               |  |

57

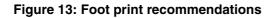

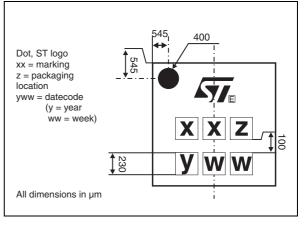

Figure 12: FLIP-CHIP Package Mechanical Data

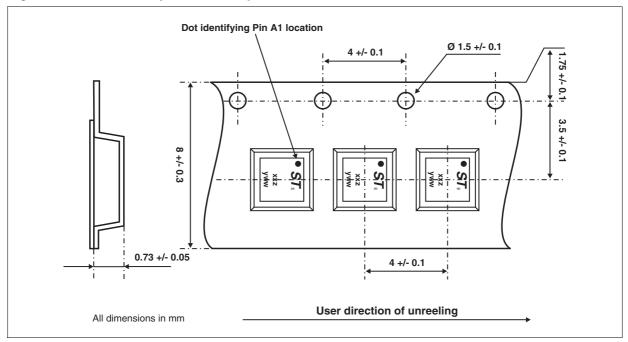

## Figure 15: FLIP-CHIP Tape and Reel Specification

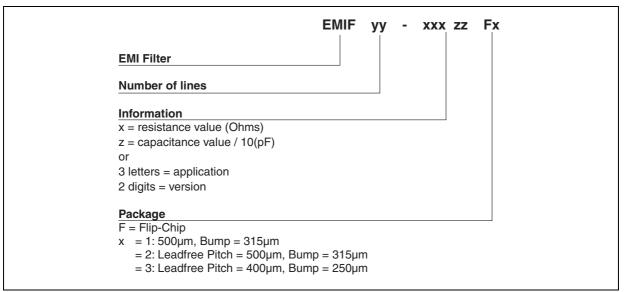

## **Table 4: Ordering Information**

| Ordering code   | Marking | Package   | Weight | Base qty | Delivery mode  |

|-----------------|---------|-----------|--------|----------|----------------|

| EMIF010-1K010F2 | FD      | Flip-Chip | 9.2 mg | 5000     | Tape & reel 7" |

**Note:** More informations are available in the application notes: AN1235: "Flip-Chip: Package description and recommendations for use" AN1751: "EMI Filters: Recommendations and measurements"

### **Table 5: Revision History**

| Date        | Revision | Description of Changes |

|-------------|----------|------------------------|

| 12-Oct-2004 | 1        | First issue            |

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners

© 2004 STMicroelectronics - All rights reserved

#### STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America www.st.com