Distributed by:

AMECO

ELECTRONICS

## www.Jameco.com + 1-800-831-4242

The content and copyrights of the attached material are the property of its owner.

Jameco Part Number 51692OKI

# **OKI** Semiconductor

This version: Jan. 1998 Previous version: Nov. 1996

# MSM80C48/49/50 MSM80C35/39/40

CMOS 8-Bit Microcontroller

### **GENERAL DESCRIPTION**

The OKI MSM80C48/MSM80C49/MSM80C50 are 8-bit, low-power, high-performance microcontrollers implemented in silicon-gate complementary metal-oxide semiconductor technology. Integrated within these chips are 8K/16K/32K bits of mask program ROM, 512/1024/2048 bits of data RAM,  $27\,I/O$  lines, built-in 8 bit timer/counter, and oscillator. Program memory and data paths are byte wide. Eleven new instructions have been added to the NMOS version's instruction set, thereby optimizing power down, port data transfer, decrement and port float functions. Available in 40-pin plastic DIP (RS) or 44-pin plastic flat packages QFP (GSK).

### **FEATURES**

Lower power consumption enabled by CMOS silicon gate process

Completely static operation

Improved power-down feature

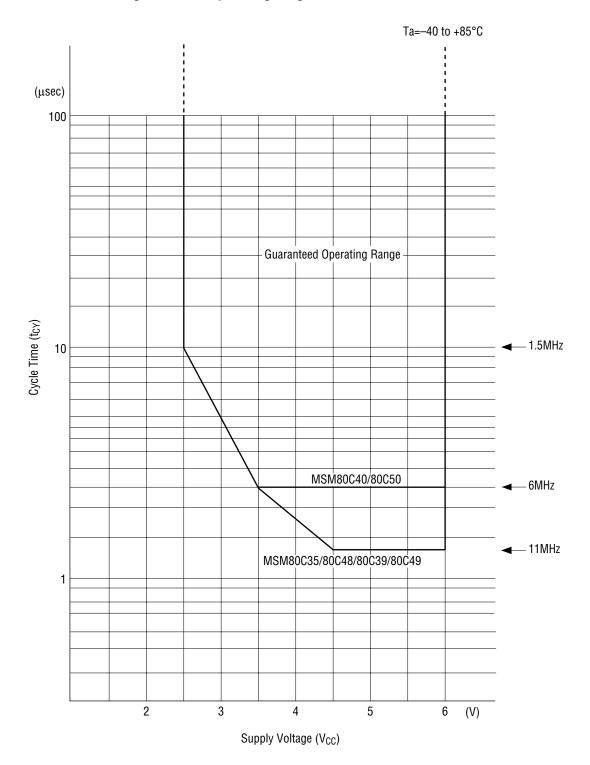

• Instruction cycle :  $1.36 \,\mu s$  (11 MHz)  $V_{CC}$ =4.5 to 6.0 V (MSM80C48/49) 2.5  $\,\mu s$  (6 MHz)  $V_{CC}$ =3.5 to 6.0 V (MSM80C50)

• 111 instructions

• All instructions are usable even during execution of external ROM instructions.

Operation facility

Addition, logical operations, and decimal adjust

Program memory (ROM)

1K words × 8 bits (MSM80C48)

:  $2K \text{ words} \times 8 \text{ bits (MSM80C49)}$

:  $4K \text{ words} \times 8 \text{ bits (MSM80C50)}$

• Data memory (RAM) : 64 words × 8 bits (MSM80C48)

: 128 words × 8 bits (MSM80C49)

: 256 words × 8 bits (MSM80C50)

Two sets of working registers

External and timer interrupts

Two test inputs

• Built-in 8-bit timer counter

• Extendable external memory and I/O ports

• I/O port

Input-output port :  $2 \text{ ports} \times 8 \text{ bits}$ Data bus input-output port :  $1 \text{ port} \times 8 \text{ bits}$

• Single-step execution function

$\bullet$  Wide range of operating voltage, from + 2.5 V to + 6 V of  $V_{CC}$

High noise margin action

• Compatible with Intel's 8048, 8049 and 8050

Package

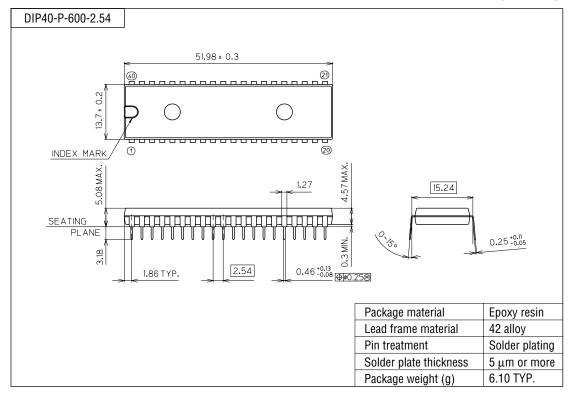

40-pin plastic DIP (DIP40-P-600-2.54) : (MSM80C48-×××RS)

(MSM80C49-xxxRS) (MSM80C50-xxxRS) (MSM80C35RS) (MSM80C39RS)

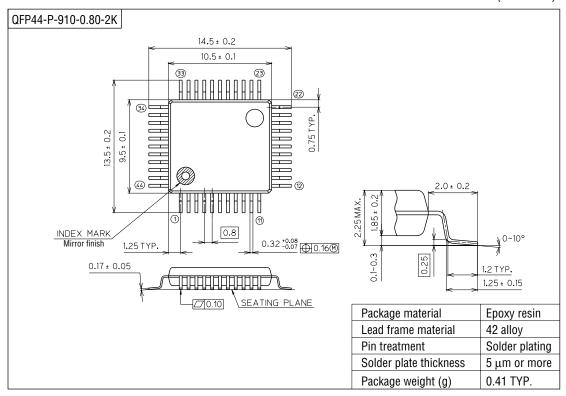

(MSM80C40RS) 44-pin plastic QFP(QFP44-P-910-0.80-2K) : (MSM80C48-xxxGS-2K)

> (MSM80C49-xxxGS-2K) (MSM80C50-xxxGS-2K) (MSM80C35GS-2K) (MSM80C39GS-2K) (MSM80C40GS-2K)

××× indicates the code number.

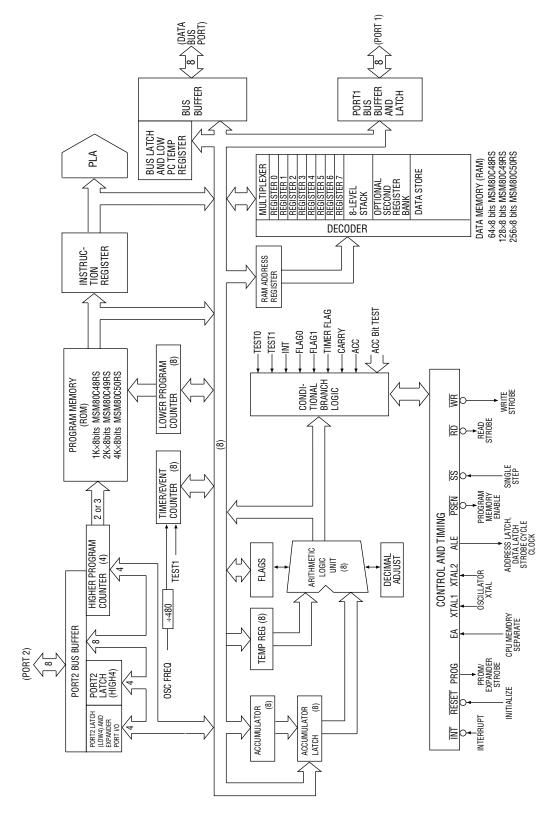

### **BLOCK DIAGRAM**

## **PIN CONFIGURATION (TOP VIEW)**

3/20

## **PIN DESCRIPTIONS**

| Symbol                                       | Type | Description                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|----------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| P1 <sub>0</sub> -P1 <sub>7</sub><br>(PORT 1) | 1/0  | 8-bit quasi-bidirectional port                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| P2 <sub>0</sub> -P2 <sub>7</sub><br>(PORT 2) | I/O  | 8-bit quasi-bidirectional port The high-order four bits of external program memory addresses can be output from P2.0-P2.3, to which the I/O expander MSM82C43RS may also be connected.                                                                                                                                                                                                                         |  |  |

| DB <sub>0</sub> -DB <sub>7</sub><br>(BUS)    | 1/0  | Bidirectional port The low-order eight bits of external program memory address can be output from this port, and the addressed instruction is fetched under the control of PSEN signal. Also, the external data memory address is output, and data is read and written synchronously using RD and WR signals. The port can also serve as either a statically latched output port or a non-latching input port. |  |  |

| T0<br>(Test 0)                               | 1/0  | The input can be tested with the conditional jump instructions JTO and JNTO. The execution of the ENTO CLK instruction causes a clock output.                                                                                                                                                                                                                                                                  |  |  |

| T1<br>(Test 1)                               | I    | The input can be tested with the conditional jump instructions JT1 and JNT1. The execution of a STRT CNT instruction causes an internal counter input.                                                                                                                                                                                                                                                         |  |  |

| INT<br>(Interrupt)                           | I    | Interrupt input. If interrupt is enabled, $\overline{\text{INT}}$ input initiates an interrupt. Interrupt is disabled after a reset.  Also testable with a JNI instruction. Can be used to terminate the power-down mode. (Active "0" level)                                                                                                                                                                   |  |  |

| RD<br>(Read)                                 | 0    | A signal to read data from external data memory. (Active "0" level)                                                                                                                                                                                                                                                                                                                                            |  |  |

| WR<br>(Write)                                | 0    | A signal to write data to external data memory. (Active "0" level)                                                                                                                                                                                                                                                                                                                                             |  |  |

| ALE<br>Address &<br>Data Latch<br>Clock      | 0    | This signal is generated in each cycle. It may be used as a clock output. External data memory or external program memory is addressed upon the falling edge. For the external ROM, this signal is used to latch the bus port data upon the ALE signal rise-up after the execution of the OUTL BUS, A instruction.                                                                                             |  |  |

| PSEN Program<br>Store Enable                 | 0    | A signal to fetch an instruction from external program memory (Active "0" level)                                                                                                                                                                                                                                                                                                                               |  |  |

| RESET                                        | I    | RESET input initialize the processor. (Active "0" level) Used to terminate the power-down mode.                                                                                                                                                                                                                                                                                                                |  |  |

| SS<br>(Single Step)                          | I    | A program is executed step by step. This pin can also be used to control internal oscillation when the power-down mode is reset. (Active "0" level)                                                                                                                                                                                                                                                            |  |  |

| EA<br>(External Access)                      | I    | When held at high level, all instructions are fetched from external memory. (Active "1" level)                                                                                                                                                                                                                                                                                                                 |  |  |

| PROG<br>(Expander Strobe)                    | 0    | This output strobes the MSM82C43RS I/O expander.                                                                                                                                                                                                                                                                                                                                                               |  |  |

## **PIN DESCRIPTIONS (Continued)**

| Symbol               | Туре | Description                                                                                                                     |

|----------------------|------|---------------------------------------------------------------------------------------------------------------------------------|

| XTAL1<br>(Crystal 1) | I    | One side of the internal crystal oscillator. An external clock can also be input.                                               |

| XTAL2<br>(Crystal 2) | 0    | Other side of the internal crystal oscillator.                                                                                  |

| V <sub>CC</sub>      | _    | Power supply pin                                                                                                                |

| V <sub>DD</sub>      | _    | Standby control input. Normally, "1" level. When set to "0" level, oscillation is stopped and prosessor goes into standby mode. |

| V <sub>SS</sub>      | _    | GND                                                                                                                             |

Note: A minimum of two machine cycles are required in  $\overline{\text{RESET}}$  pulse duration under the specified power supply and stable oscillator frequency.

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter           | Symbol           | Condition | Rating                       | Unit |

|---------------------|------------------|-----------|------------------------------|------|

| Supply Voltage      | V <sub>CC</sub>  | Ta=25°C   | –0.5 to 7                    | V    |

| Input Voltage       | VI               | Ta=25°C   | -0.3 to V <sub>CC</sub> +0.5 | V    |

| Storage Temperature | T <sub>STG</sub> | _         | -65 to +150                  | °C   |

## **RECOMMENDED OPERATING CONDITIONS**

| Parameter           | Symbol Condition |                                | Range      | Unit |

|---------------------|------------------|--------------------------------|------------|------|

| Supply Voltage      | V <sub>CC</sub>  | f <sub>OSC</sub> =DC to 11MHz* | +2.5 to +6 | V    |

| Ambient Temperature | Ta               | _                              | -40 to +85 | °C   |

| Fan Out             | N                | MOS load                       | 10         | _    |

| Fan Out             | N                | TTL load                       | 1          | _    |

<sup>\*</sup> Minimum operating voltage is dependent on frequency.

## MSM80C48/49/50 guaranteed operating range

## **ELECTRICAL CHARACTERISTICS**

### **DC Characteristics**

$(V_{CC}=5 V\pm 10\%, Ta=-40 to +85^{\circ}C)$

| Parameter                        | Symbol                            | Condition                                                    | Min.                 | Тур. | Max.                 | Unit | Mea-<br>suring<br>Circuit |

|----------------------------------|-----------------------------------|--------------------------------------------------------------|----------------------|------|----------------------|------|---------------------------|

| "L" Input Voltage                | V <sub>IL</sub>                   | _                                                            | -0.5                 | _    | 0.13 V <sub>CC</sub> | V    |                           |

| "H" Input Voltage *1             | V <sub>IH</sub>                   |                                                              | 0.4 V <sub>CC</sub>  | _    | V <sub>CC</sub>      | V    |                           |

| "H" Input Voltage *2             | V <sub>IH</sub>                   | _                                                            | 0.7 V <sub>CC</sub>  | _    | Vcc                  | V    |                           |

| "L" Output Voltage *3            | V <sub>OL</sub>                   | I <sub>OL</sub> =2 mA                                        | _                    |      | 0.45                 | V    | ]                         |

| "L" Output Voltage *4            | V <sub>OL</sub>                   | I <sub>OL</sub> =1.6 mA                                      | _                    | _    | 0.45                 | V    | 1                         |

| "H" Output Voltage *3            | V <sub>OH</sub>                   | I <sub>OH</sub> =-400 μA                                     | 0.75 V <sub>CC</sub> | _    | _                    | V    |                           |

| "H" Output Voltage *4            | V <sub>OH</sub>                   | I <sub>OH</sub> =-50 μA                                      | 0.75 V <sub>CC</sub> | _    | _                    | V    |                           |

| "H" Output Voltage *3            | V <sub>OH</sub>                   | I <sub>OH</sub> =-20 μA                                      | 0.93 V <sub>CC</sub> | _    | _                    | ٧    |                           |

| "H" Output Voltage *4            | V <sub>OH</sub>                   | I <sub>OH</sub> =-10 μA                                      | 0.93 V <sub>CC</sub> | _    | _                    | V    |                           |

| Input Leakage Curent             | I <sub>IL</sub>                   | $V_{SS} \le V_{IN} \le V_{CC}$                               | _                    | _    | ±5                   | μΑ   | 2                         |

| Output Leakage Current *5        | I <sub>OL</sub>                   | $V_{SS} \le V_0 \le V_{CC}$                                  | _                    | _    | ±5                   | μΑ   | 3                         |

| DECET Input ourrent              | I_                                | V <sub>IN</sub> =0.7 V <sub>CC</sub>                         | -20                  | -50  | -80                  | μΑ   |                           |

| RESET Input current              | I <sub>R</sub>                    | V <sub>IN</sub> =0.13 V <sub>CC</sub>                        | -3                   | -8   | -15                  | μΑ   | 2                         |

| CC Input ourrant *C              | 1                                 | Pull-up (V <sub>IN</sub> =V <sub>IL</sub> )                  | 20                   | 50   | 80                   | μΑ   | 2                         |

| SS Input current *6              | I <sub>SS</sub>                   | Pull-down (V <sub>IN</sub> =V <sub>IH</sub> )                | -6                   | -15  | -25                  | μΑ   | ]                         |

| D1 D2 input ourrant              | I <sub>P1</sub> , I <sub>P2</sub> | V <sub>IN</sub> =V <sub>IH</sub>                             | -300                 | -600 | -900                 | μΑ   | 0                         |

| P1, P2 input current             |                                   | V <sub>IN</sub> =V <sub>IL</sub>                             | -10                  | -40  | -80                  | μΑ   | 2                         |

| Power Down Mode                  | I <sub>CCS</sub>                  | At hardware power down *7<br>Ta=25°C, V <sub>CC</sub> =2.0 V | _                    | _    | 10                   |      |                           |

| Standby Current                  |                                   | At HLTS execution *7<br>Ta=25°C, V <sub>CC</sub> =2.0 V      | _                    | _    | 10                   | μА   |                           |

|                                  | Icc                               | V <sub>CC</sub> =4 V, f=1 MHz                                | —                    | _    | 0.5                  |      |                           |

|                                  |                                   | V <sub>CC</sub> =4 V, f=6 MHz                                | _                    | _    | 1.0                  |      |                           |

|                                  |                                   | V <sub>CC</sub> =4 V, f=11 MHz                               | _                    | _    | 2.0                  |      |                           |

| Dower Cumply Current             |                                   | V <sub>CC</sub> =5 V, f=1 MHz                                | _                    |      | 1.0                  |      |                           |

| Power Supply Current (Halt Mode) |                                   | V <sub>CC</sub> =5 V, f=6 MHz                                | _                    | _    | 2.0                  | mA   |                           |

| (Hair Mode)                      |                                   | V <sub>CC</sub> =5 V, f=11 MHz                               | _                    | _    | 3.0                  |      |                           |

|                                  |                                   | V <sub>CC</sub> =6 V, f=1 MHz                                | _                    | _    | 1.5                  |      |                           |

|                                  |                                   | V <sub>CC</sub> =6 V, f=6 MHz                                | _                    | _    | 3.0                  |      | 4                         |

|                                  |                                   | V <sub>CC</sub> =6 V, f=11 MHz                               | _                    | _    | 5.0                  |      |                           |

|                                  |                                   | V <sub>CC</sub> =4 V, f=1 MHz                                | _                    | _    | 1.5                  |      |                           |

|                                  |                                   | V <sub>CC</sub> =4 V, f=6 MHz                                | _                    | _    | 5.0                  |      |                           |

|                                  |                                   | V <sub>CC</sub> =4 V, f=11 MHz                               | _                    | _    | 10                   |      |                           |

|                                  |                                   | V <sub>CC</sub> =5 V, f=1 MHz                                | _                    | _    | 2.5                  |      |                           |

| Power Supply Current             | t I <sub>CC</sub>                 | V <sub>CC</sub> =5 V, f=6 MHz                                | _                    | _    | 7.5                  | mA   |                           |

|                                  |                                   | V <sub>CC</sub> =5 V, f=11 MHz                               | _                    | _    | 15                   |      |                           |

|                                  |                                   | V <sub>CC</sub> =6 V, f=1 MHz                                | _                    | _    | 5.0                  |      |                           |

|                                  | -                                 | V <sub>CC</sub> =6 V, f=6 MHz                                | _                    | _    | 10                   |      |                           |

|                                  |                                   | V <sub>CC</sub> =6 V, f=11 MHz                               | _                    | _    | 20                   |      |                           |

- \*1 This does not apply to RESET, XTAL1, XTAL2,  $V_{DD}$ , and EA.

- \*2 RESET, XTAL1, XTAL2, V<sub>DD</sub>, and EA.

- \*3 BUS, RD, WR, PSEN, ALE, PROG

- \*4 Other outputs

- \*5 High-impedance state

- \*6 This operates as a pull-down resistor when the oscillation is stopped in the HLTS or  $V_{DD}$  power-down mode and as a pull-up resistor in other states.

- \*7 This does not contain flow out current from I/O ports and signal pins.

### **AC Characteristics**

(V<sub>CC</sub>=2.5V to 6V (\*1), Ta=-40 to +85°C)

|                                                                  |                    | V <sub>CC</sub> =5 V±10% |      | Variabl     |         |      |

|------------------------------------------------------------------|--------------------|--------------------------|------|-------------|---------|------|

| Parameter                                                        | Symbol             | 11 MHz Clock             |      | 0 to 11 MHz |         | Unit |

|                                                                  |                    | Min.                     | Max. | Min.        | Max.    |      |

| ALE Pulse Width                                                  | t <sub>LL</sub>    | 150                      | _    | 3.5t-170    | _       | ns   |

| Address Setup Time (up to ALE)                                   | t <sub>AL</sub>    | 70                       | _    | 2t-110      | _       | ns   |

| Address Hold Time (from ALE)                                     | t <sub>LA</sub>    | 50                       | _    | t-40        | _       | ns   |

| Bus Port Latch Data Setup Time (up to ALE Rising Edge)           | t <sub>BL</sub>    | 110                      | _    | 2.5t -115   | _       | ns   |

| Bus Port Latch Data Hold Time (from ALE Rising Edge)             | t <sub>LB</sub>    | 90                       | _    | 1.5 t-45    | _       | ns   |

| Control Pulse Width (RD, WR)                                     | t <sub>CC1</sub>   | 480                      | _    | 7t-155      | _       | ns   |

| Control Pulse Width (PSEN)                                       | t <sub>CC2</sub>   | 350                      | _    | 6t-200      | _       | ns   |

| Data Setup Time (before WR)                                      | t <sub>DW</sub>    | 390                      | _    | 6t-155      | _       | ns   |

| Data Hold after Time (after WR)                                  | t <sub>WD</sub>    | 40                       | _    | 2t-140      | _       | ns   |

| Data Hold Time (after RD, PSEN)                                  | t <sub>DR</sub>    | 0                        | 110  | 0           | 1.5t-30 | ns   |

| RD to Data-in                                                    | t <sub>RD1</sub>   | _                        | 350  | _           | 5t-265  | ns   |

| PSEN to Data-in                                                  | t <sub>RD2</sub>   | _                        | 190  | _           | 5t-265  | ns   |

| Address Setup to WR                                              | t <sub>AW</sub>    | 300                      | _    | 6t-245      | _       | ns   |

| Address Setup to Data-in                                         | t <sub>AD1</sub>   | _                        | 730  | _           | 12t-360 | ns   |

| Address Setup to Instruction                                     | t <sub>AD2</sub>   | _                        | 460  | _           | 8t-265  | ns   |

| Address Float to $\overline{\text{RD}}$ , $\overline{\text{WR}}$ | t <sub>AFC1</sub>  | 140                      | _    | 2t-40       | _       | ns   |

| Address Float to PSEN                                            | t <sub>AFC2</sub>  | 10                       | _    | 10          | _       | ns   |

| Control Pulse Setup Time from ALE (PSEN)                         | t <sub>LAFC2</sub> | 60                       | _    | t-30        | _       | ns   |

| Control Pulse Setup Time from ALE (RD, WR)                       | t <sub>LAFC1</sub> | 200                      | _    | 3t-75       | _       | ns   |

| Control Pulse up to ALE (RD, WR, PROG)                           | t <sub>CA1</sub>   | 50                       | _    | 1.5t-85     | _       | ns   |

| Control Pulse up to ALE (PSEN)                                   | t <sub>CA2</sub>   | 320                      | _    | 4.5t-90     | _       | ns   |

| Port Control Setup Time (up to PROG Falling Edge)                | t <sub>CP</sub>    | 50                       | _    | 2t-130      | _       | ns   |

| Port Control Hold Time (from PROG Falling Edge)                  | t <sub>PC</sub>    | 100                      | _    | 4t-260      | _       | ns   |

| PROG to Input Data Valid                                         | t <sub>PR</sub>    | _                        | 650  | _           | 9t-170  | ns   |

| Input Data Hold Time                                             | t <sub>PF</sub>    | 0                        | 140  | 0           | 1.5t    | ns   |

| Output Data Setup Time                                           | t <sub>DP</sub>    | 250                      | _    | 6t-290      | _       | ns   |

| Output Data Hold Time                                            | t <sub>PD</sub>    | 40                       | _    | 3t-230      | _       | ns   |

| PROG Pulse Width                                                 | t <sub>PP</sub>    | 700                      | _    | 10t-210     | _       | ns   |

| Port 2 I/O Setup Time                                            | t <sub>PL</sub>    | 160                      | _    | 4.5-250     | _       | ns   |

| Port 2 I/O Hold Time                                             | t <sub>LP</sub>    | 15                       | _    | 1.5t-120    | _       | ns   |

| Port Output Data (from ALE)                                      | t <sub>PV</sub>    | _                        | 510  | _           | 4t+145  | ns   |

| TO Cycle                                                         | toprr              | 270                      | _    | 3t          | _       | ns   |

| Instruction Execution Time                                       | t <sub>CY</sub>    | 1.36                     | _    | 15t         | _       | μs   |

Note: Control output:  $C_L=80pF$

Bus output :  $C_L=150$ pF [for 20 pF ( $t_{AL}$ ,  $t_{AFC1}$ ,  $t_{AFC2}$ )]

<sup>\*1</sup> Minimum operating voltage is dependent on frequency.

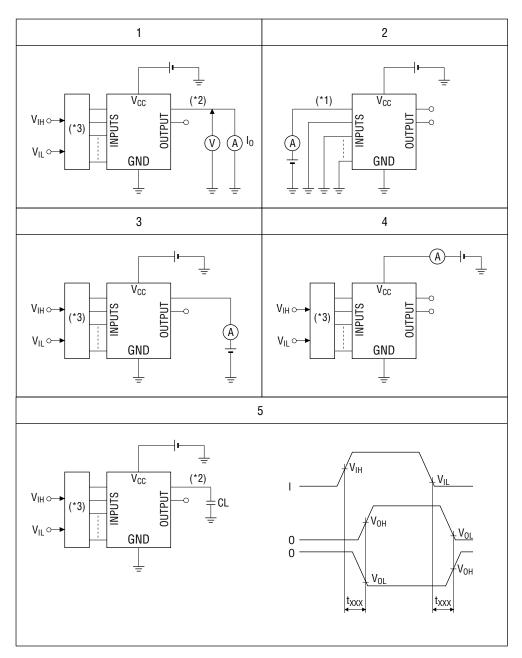

### **Measuring circuits**

- \*1 This is repeated for each specified input pin.

- \*2 This is repeated for each specified output pin.

- \*3 Input logic for setting the specified state

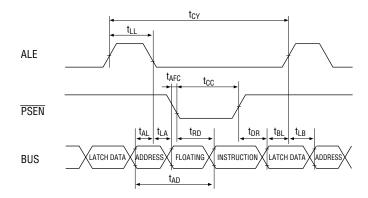

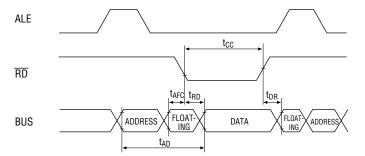

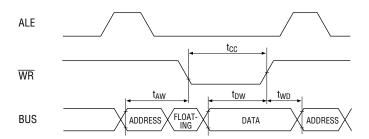

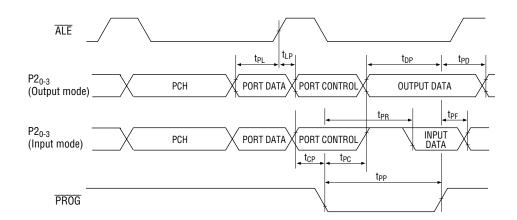

### **Timing Diagram**

## Instruction fetch (from external program memory)

## Read (from external data memory)

### Write (to external memory)

# Low-order 4 bits input/output of port 2 when expanded I/O port is used (in external program memory access mode)

### **FUNCTIONAL DESCRIPTION**

### Added Functions of MSM80C48, MSM80C49 and MSM80C50

The MSM80C48, MSM80C49 and MSM80C50 are basically incorporated with the capabilities of Intel's 8048, 8049, and 8050 plus the following new functions:

### 1. Power-Down Mode Enhancements

### 1.1 Power-down by software

- (1) Clock (See item 4, "Power-down mode", for details.)

- Crystal oscillator halt (HLTS instruction) Power requirements can be minimized.

- Clock supply halt (HALT instruction) Restart is accomplished without oscillator wait.

- (2) I/O ports

I/O port floating instructions

Power consumption resulting from inputs/outputs can be minimized with FLT and FLTT instructions.

Port floating is cancelled by executing FRES instruction, "0" level at INT pin or "0" level at RESET pin.

(3) Six types of power-down can be done by a combination of HLTS/HALT and FLT/FLTT instructions.

# 1.2 Power-down by hardware (See 4.3, Power-down mode by V<sub>DD</sub> pin utilization for

Crystal oscillators can be halted by controlling the V<sub>DD</sub> pin, thereby floating all I/O ports for minimum power consumption.

### 2. Additional Instructions (11)

HLTS MOV A, P2 HALT MOVP1, @ R3 FLT MOVP1 P, @R3 FLTT DEC @Rr FRES DJNZ @ Rr, addr MOV A, P1

## Improved Uses of BUS P<sub>0</sub>-7, P1<sub>0</sub>-7, P2<sub>0</sub>-7, and SS pins

### 3.1 BUS P<sub>0</sub>-7

The MSM80C48, MSM80C49, and MSM80C50 remove the limitation on the use of OUTL BUS, A instructions during the external ROM access mode by having an independent data latch and external ROM mode address latch in BUS  $P_{0-7}$ .

Consequently, there is no need to relocate bus port instructions when in the external ROM access mode.

### 3.2 P<sub>10</sub>-7 and P2<sub>0</sub>-7

The MSM80C48, MSM80C49 and MSM 80C50 are designed to minimize power consumption when P1<sub>0-7</sub> and P2<sub>0-7</sub> are used as input/output ports, to maximize the performance of CMOS.

When these ports are used as output ports, the acceleration circuit is actuated only when

output data changes from "0" to "1", thus speeding up the rise time of the output signals. When these ports are used as input ports, the internal pull-up resistor becomes approximately 9 k $\Omega$  when input data is "1".

The internal pull-up resistor rises to approximately 100 k $\Omega$  when input data is "0".

Thus, a high noise margin can be obtained by selecting the impedance and thus the outflow of current is minimized whenever these ports are used as output or input ports.

### 3.3 Clock generation control via the SS pin

When the crystal oscillator is halted in the HLTS or hardware power-down mode, the  $\overline{SS}$  pin is pulled down by a resistor of 20 to 50 k $\Omega$ , while its internal pull-up resistor of 200 to  $500k\Omega$  is isolated from  $V_{CC}$ . When the power-down mode is cancelled, the internal resistor of the  $\overline{SS}$  pin is changed from pull-down to pull-up. Consequently, the CPU can be halted for any period of time until the crystal oscillator resumes normal oscillation when a capacitor is connected to the  $\overline{SS}$  pin.

#### 4. Power-Down Mode

The MSM80C48, MSM80C49, and MSM80C50 power-down mode can be enabled in two different ways through software by a combination of clock control and port floating instructions, and through hardware by control of the  $V_{DD}$  pin.

### 4.1 Software power-down mode

Power-down mode can be done by a combination of the following instructions.

(1) HALT (clock supply halt to control circuit)

Instruction code : 0 0 0 0 0 0 1

Description: Although crystal oscillator operation is continued, the clock supply to

the CPU control circuit is halted and CPU operations are suspended. When cancelling this software mode, restart is accomplished without

oscillator wait.

(2) HLTS (oscillation stop)

Instruction code : 1 0 0 0 0 0 1 0

Description: The oscillator operation is halted and CPU operations are suspended. In

cancelling this power down mode, connecting a capacitor to the  $\overline{SS}$  pin enables a reasonable wait period to be accomplished before normal operation is resumed. [Except in the case of using the  $\overline{RESET}$  pin]

(3) FLT (floating  $P1_{0-7}$ ,  $P2_{0-7}$ , and  $BP_{0-7}$ )

Instruction code: 1 0 1 0 0 0 1 0

Description:

|    | Internal ROM mode | External ROM mode            |  |

|----|-------------------|------------------------------|--|

| P1 | Floating          | Floating                     |  |

| P2 | Floating          | P2 <sub>0</sub> -3 operation |  |

| BP | Floating          | Operation                    |  |

Details of IC pin status as a result of executing the FLT instruction are shown in the above table.

(4) FLTT (floating of all output pins)

Instruction code: 1 1 0 0 0 0 1 0

Description:

|        | Internal ROM mode | External ROM mode            |  |

|--------|-------------------|------------------------------|--|

| ALE    | Floating          | Operation                    |  |

| PSEN   | Floating          | Operation                    |  |

| PROG   | Floating          | Floating                     |  |

| WR     | Floating          | Floating                     |  |

| PD     | Floating          | Floating                     |  |

| TO OUT | Floating          | Floating                     |  |

| P1     | Floating          | Floating                     |  |

| P2     | Floating          | P2 <sub>0</sub> -3 operation |  |

| ВР     | Floating          | Operation                    |  |

| XTAL   | Operation         | Operation                    |  |

Details of IC pin status as a result of executing the FLTT instruction are shown in above Table.

- Example 1: Power-down mode accomplished by stopping oscillation.

- O Can be set by execution of HLTS [82H] instruction.

- Example 2: Power-down mode accomplished by stopping the clock supply to the CPU control circuit.

- O Can be set by execution of HALT [01H] instruction.

- Example 3: Power-down mode by floating of P1<sub>0-7</sub>, P2<sub>0-7</sub> and BP<sub>0-7</sub>, and subsequent stopping of CPU oscillation.

- O Can be set by first executing the FLT [A2H] instruction, followed by the HLTS [82H] instruction.

- Example 4: Power-down mode by floating P1<sub>0-7</sub>, P2<sub>0-7</sub> and BP<sub>0-7</sub>, and then stopping the clock supply to the CPU control circuit.

- O Can be set by first executing the FLT [A2H] instruction, and then the HALT [01H] instruction.

- $Example\ 5:\ Power-down\ mode\ by\ floating\ all\ output\ pins, followed\ by\ stopping\ oscillation.$

- O Can be set by first executing the FLTT [C2H] instruction followed by execution of the HLTS [82H] instruction.

- Example 6: Power-down mode by floating all output pins, followed by stopping of the clock supply to the CPU control circuit.

- O Can be set by first executing the FLTT [C2H] instruction, followed by execution of the HALT [01H] instruction. Connect the pull-up resistor or pull-down resistor to port pin and fix the output port pin level to either 1 or 0 when output port is set to floating.

### 4.2 Cancellation of software power-down mode

The power-down mode status outlined above in examples 1 to 6 can be cancelled by using either the interrupt pin or the RESET pin.

- (1) Use of the  $\overline{\text{INT}}$  pin during external interrupt enable mode (i.e. following execution of EN I instruction).

- O The clock generator is activated and the CPU is started up when a "0" level is applied to the INT pin. If this "0" level is maintained until the occurrence of at least 2 ALE output signals, an external interrupt is generated, and execution proceeds from address 3. If, however, the power-down is entered during the interrupt processing routine, execution resumes just after the power-down instruction.

- (2) Use of the <u>INT</u> pin during external interrupt disable mode (i.e. following execution of DIS I instruction or hardware reset)

- O The clock generator is activated and the CPU is started up when a "0" level is applied to the INT pin. When "0" level is maintained until the occurrence of at least 2 ALE output signals, execution is resumed just after the power-down instruction.

- (3) Use of the  $\overline{RESET}$  pin

- O The clock generator is activated and the CPU started up when a "0" level is applied to the  $\overline{\text{RESET}}$  pin. If this "0" level is maintained until the occurrence of at least 2 ALE output signals, the CPU is reset and execution proceeds from address 0. In case cancellation is done in oscillation stop mode, the "0" level must be input to the  $\overline{\text{RESET}}$  pin until oscillation is stabilized.

### 4.3 Hardware power-down mode

In the MSM80C48, MSM80C49 and MSM80C50, forcing the level at the  $V_{DD}$  pin to a "0" during either external ROM or internal ROM mode results in suspension of the oscillator function and subsequent floating (high impedance) of all the I/O pins except the  $\overline{RESET}$ ,  $\overline{SS}$  and XTAL 1/2 pins. The CPU is thereby stopped while maintaining internal status.

### 4.4 Cancellation of hardware power-down mode

- (1) Use of  $\overline{RESET}$  pin

- O The clock generator is activated and the CPU started up when a "1" level is applied to the  $V_{DD}$  pin while a "0" level is input to the  $\overline{RESET}$  pin. If this "0" level is kept applied to the  $\overline{RESET}$  pin until oscillation become stable, the CPU will be reset and will start executing from address 0.

- (2) Use of the INT pin during external interrupt enable status (i.e. following execution of EN I instruction)

- O The clock generator is activated and the CPU started up when a "1" level is applied to the V<sub>DD</sub> pin while a "0" level is applied to the INT pin. If this "0" level is maintained until the occurrence of at least 2 ALE output signals, an external interrupt is generated, and execution starts from address 3.

- However, if the power-down mode is started during an interrupt processing routine, execution will be continued on the next instruction after the present instruction.

- (3) Use of the INT pin during external interrupt disable mode (i.e. following excution of DIS I instruction or hardware reset)

- O The clock generator is activated and the CPU started up when a "1" level is applied to the V<sub>DD</sub> pin while a "0" level is applied to the INT pin. If this "0" level is maintained until the occurrence of at least 2 ALE output signals, execution is continued on the next instruction after the present instruction.

- (4) Use of V<sub>DD</sub> pin only

- O The clock generator is activated and the CPU started up when a "1" level is applied to the V<sub>DD</sub> pin while a "1" level is also applied to both the RESET and INT pins. In this case, execution is resumed from the stopped position.

### **PACKAGE DIMENSIONS**

(Unit: mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

(Unit: mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage. Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).