# **TDA8953**

2 × 210 W class-D power amplifier Rev. 01 — 24 December 2009

#### **General description** 1.

The TDA8953 is a stereo or mono high-efficiency Class D audio power amplifier in a single IC featuring low power dissipation. It is designed to deliver up to  $2 \times 210$  W into a 4  $\Omega$  load in a stereo Single-Ended (SE) application, or 1 × 420 W into an 8  $\Omega$  load in a mono Bridge-Tied Load (BTL) application.

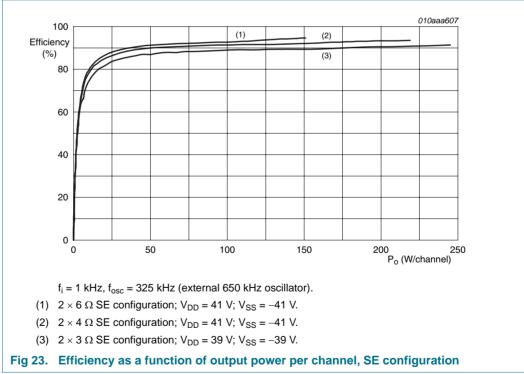

It combines the benefits of Class D efficiency ( $\approx$ 93 % into a 4  $\Omega$  load) with audiophile sound quality comparable to that associated with Class AB amplification.

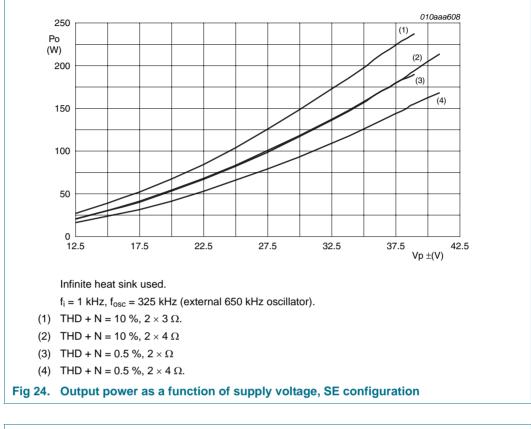

The amplifier operates over a wide supply voltage range from  $\pm 12.5$  V to  $\pm 42.5$  V and features low quiescent current consumption.

#### 2. **Features**

- High output power in typical applications:

- SE 2 × 210 W,  $R_1 = 4 \Omega (V_{DD} = 41 V; V_{SS} = -41 V)$

- SE 2 × 235 W,  $R_1 = 3 \Omega (V_{DD} = 39 V; V_{SS} = -39 V)$

- SE 2  $\times$  150 W, R<sub>L</sub> = 6  $\Omega$  (V<sub>DD</sub> = 41 V; V<sub>SS</sub> = -41 V)

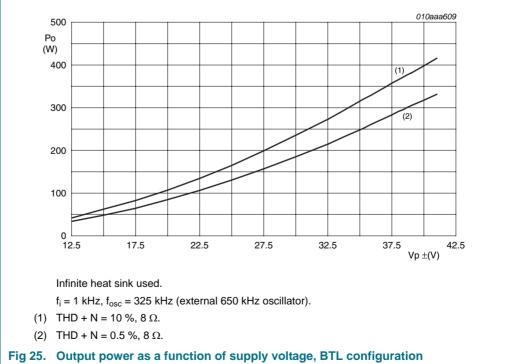

- ◆ BTL 1 × 420 W, R<sub>I</sub> = 8 Ω (V<sub>DD</sub> = 41 V; V<sub>SS</sub> = −41 V)

- Symmetrical operating supply voltage range from ±12.5 V to ±42.5 V

- Stereo full differential inputs, can be used as stereo SE or mono BTL amplifier

- Low noise

- Smooth pop noise-free start-up and switch off

- Fixed frequency internal or external clock

- High efficiency ≈93 %

- Zero dead time switching

- Low guiescent current

- Advanced protection strategy: voltage protection and output current limiting

- Thermal FoldBack (TFB) with disable functionality

- Fixed gain of 30 dB in SE and 36 dB in BTL applications

- Fully short-circuit proof across load

- BD modulation in BTL configuration

- Clock protection

#### **Applications** 3.

- DVD

- Mini and micro receiver

- Subwoofers

#### **Quick reference data** 4.

#### . . . .

- Home Theater In A Box (HTIAB) system

- High-power speaker system

- Public Address (PA) system

| Table 1.             | Quick reference data                     |                                                                                                                                                                                                                                               |            |       |     |       |      |

|----------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|-----|-------|------|

| Symbol               | Parameter                                | Conditions                                                                                                                                                                                                                                    |            | Min   | Тур | Max   | Unit |

| General              |                                          |                                                                                                                                                                                                                                               |            |       |     |       |      |

| V <sub>DD</sub>      | positive supply voltage                  | Operating mode                                                                                                                                                                                                                                | [1]        | 12.5  | 41  | 42.5  | V    |

| V <sub>SS</sub>      | negative supply voltage                  | Operating mode                                                                                                                                                                                                                                | [2]        | -12.5 | -41 | -42.5 | V    |

| V <sub>th(ovp)</sub> | overvoltage protection threshold voltage | Standby, Mute modes; $V_{DD} - V_{SS}$                                                                                                                                                                                                        |            | 85    | -   | 90    | V    |

| I <sub>DD(tot)</sub> | total positive supply current            | the sum of the currents through pins VDDA, VDDP1 and VDDP2                                                                                                                                                                                    |            | -     | 50  | 60    | mA   |

|                      |                                          | Operating mode; no load; no filter; no RC-snubber network connected;                                                                                                                                                                          |            |       |     |       |      |

| I <sub>SS(tot)</sub> | total negative supply current            | the sum of the currents through pins VSSA, VSSP1 and VSSP2                                                                                                                                                                                    |            | -     | 65  | 75    | mA   |

|                      |                                          | Operating mode; no load; no filter; no RC-snubber network connected;                                                                                                                                                                          |            |       |     |       |      |

| Stereo s             | ingle-ended configuration                |                                                                                                                                                                                                                                               |            |       |     |       |      |

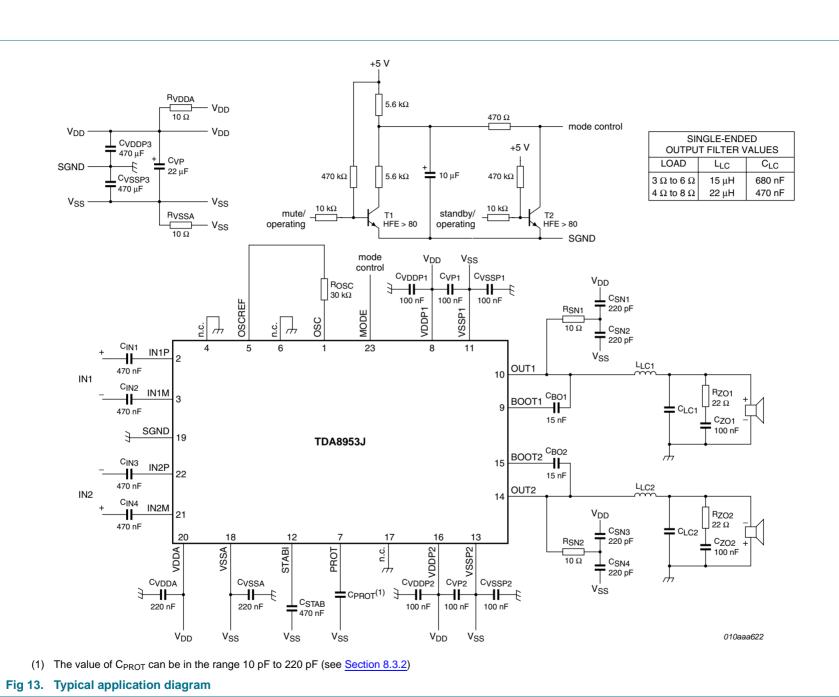

| Po                   | output power                             | $T_j$ = 85 °C; $L_{LC}$ = 15 $\mu H;$ $C_{LC}$ = 680 nF (see Figure 13)                                                                                                                                                                       |            |       |     |       |      |

|                      |                                          | THD + N = 10 %; R <sub>L</sub> = 4 $\Omega$ ; V <sub>DD</sub> = 41 V; V <sub>SS</sub> = -41 V                                                                                                                                                 | <u>[3]</u> | -     | 210 | -     | W    |

|                      |                                          | THD + N = 10 %; R <sub>L</sub> = 4 $\Omega$ ; V <sub>DD</sub> = 35 V; V <sub>SS</sub> = -35 V                                                                                                                                                 |            | -     | 150 | -     | W    |

| Mono br              | idge-tied load configuration             |                                                                                                                                                                                                                                               |            |       |     |       |      |

| Po                   | output power                             | $\begin{array}{l} T_{j} = 85 \ ^{\circ}\text{C}; \ L_{LC} = 22 \ \mu\text{H}; \ C_{LC} = 680 \ n\text{F} \ (\text{see} \\ \hline Figure \ 13); \ R_{L} = 8 \ \Omega; \ THD + N = 10 \ \%; \\ V_{DD} = 41 \ V; \ V_{SS} = -41 \ V \end{array}$ | <u>[3]</u> | -     | 420 | -     | W    |

[1] V<sub>DD</sub> is the supply voltage on pins VDDP1, VDDP2 and VDDA.

$\mathsf{V}_{\mathsf{SS}}$  is the supply voltage on pins VSSP1, VSSP2 and VSSA. [2]

Output power is measured indirectly; based on R<sub>DSon</sub> measurement; see Section 14.3. [3]

#### **Ordering information** 5.

#### Table 2. **Ordering information**

| Type number | Package | ackage                                                                     |          |  |  |  |  |  |  |

|-------------|---------|----------------------------------------------------------------------------|----------|--|--|--|--|--|--|

|             | Name    | Description                                                                | Version  |  |  |  |  |  |  |

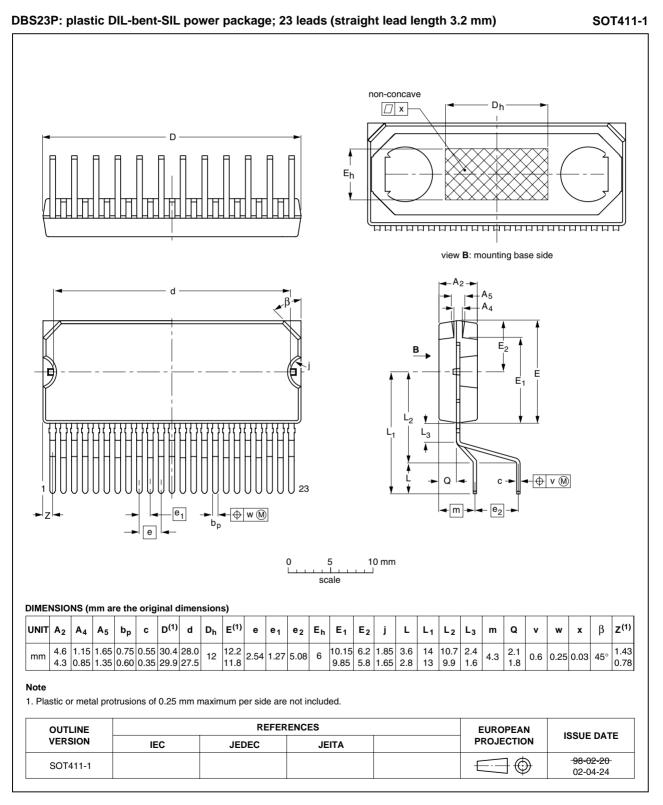

| TDA8953J    | DBS23P  | plastic DIL-bent-SIL power package; 23 leads (straight lead length 3.2 mm) | SOT411-1 |  |  |  |  |  |  |

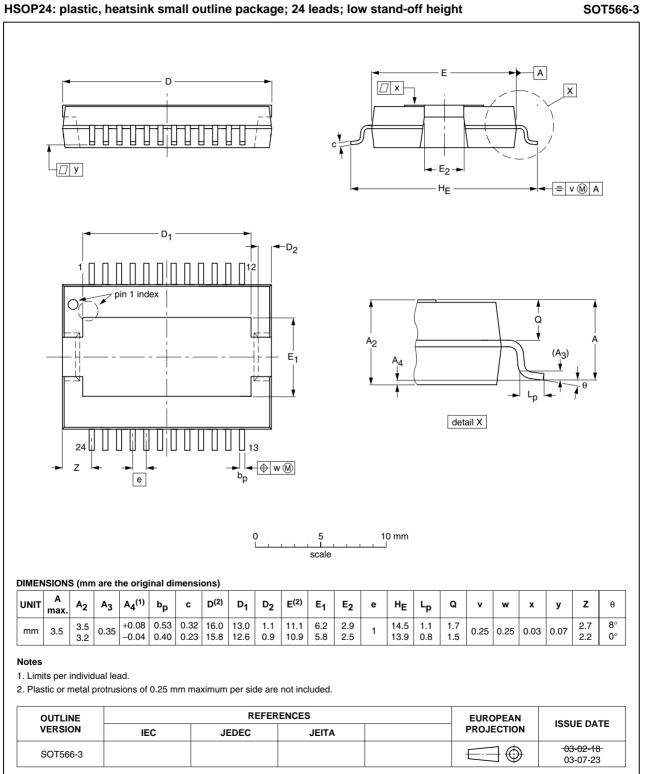

| TDA8953TH   | HSOP24  | plastic, heatsink small outline package; 24 leads; low stand-off height    | SOT566-3 |  |  |  |  |  |  |

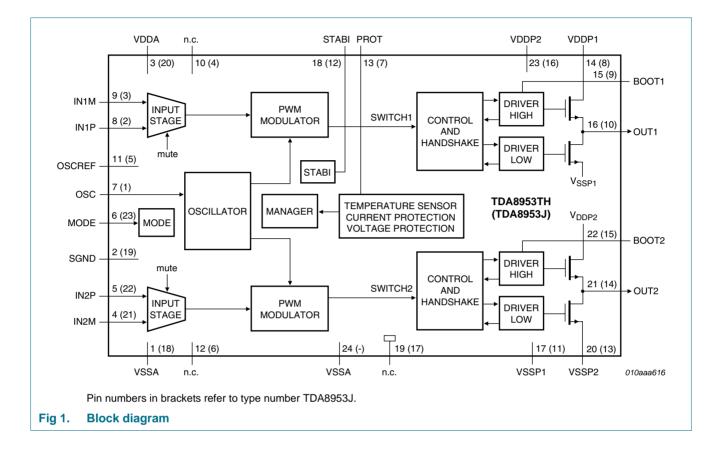

## 6. Block diagram

## 7. Pinning information

#### OSC 1 IN1P 2 IN1M 3 n.c. 4 5 OSCREF n.c. 6 PROT 7 VDDP1 8 BOOT1 9 OUT1 10 VSSP1 11 $\bigcirc$ VSSA 24 1 VSSA TDA8953J STABI 12 VDDP2 23 2 SGND VSSP2 13 BOOT2 22 3 VDDA OUT2 14 OUT2 21 4 IN2M BOOT2 15 VSSP2 20 5 IN2P VDDP2 16 6 MODE n.c. 19 n.c. 17 TDA8953TH STABI 18 7 OSC VSSA 18 VSSP1 17 8 IN1P SGND 19 OUT1 16 9 IN1M VDDA 20 BOOT1 15 10 n.c. IN2M 21 VDDP1 14 11 OSCREF IN2P 22 12 n.c. PROT 13 MODE 23 010aaa617 010aaa618 Pin configuration TDA8953TH Pin configuration TDA8953J Fig 2. Fig 3.

#### 7.1 Pinning

### 7.2 Pin description

| Table 3. | Pin descriptio | n        |                                                       |

|----------|----------------|----------|-------------------------------------------------------|

| Symbol   | Pin            |          | Description                                           |

|          | TDA8953TH      | TDA8953J |                                                       |

| VSSA     | 1              | 18       | negative analog supply voltage                        |

| SGND     | 2              | 19       | signal ground                                         |

| VDDA     | 3              | 20       | positive analog supply voltage                        |

| IN2M     | 4              | 21       | channel 2 negative audio input                        |

| IN2P     | 5              | 22       | channel 2 positive audio input                        |

| MODE     | 6              | 23       | mode selection input: Standby, Mute or Operating mode |

| OSC      | 7              | 1        | oscillator frequency adjustment or tracking input     |

| IN1P     | 8              | 2        | channel 1 positive audio input                        |

| IN1M     | 9              | 3        | channel 1 negative audio input                        |

| n.c.     | 10             | 4        | not connected                                         |

| OSCREF   | 11             | 5        | reference for OSC pin                                 |

| n.c.     | 12             | 6        | not connected                                         |

| PROT     | 13             | 7        | decoupling capacitor for protection (OCP)             |

| VDDP1    | 14             | 8        | channel 1 positive power supply voltage               |

| BOOT1    | 15             | 9        | channel 1 bootstrap capacitor                         |

| OUT1     | 16             | 10       | channel 1 PWM output                                  |

| VSSP1    | 17             | 11       | channel 1 negative power supply voltage               |

| STABI    | 18             | 12       | decoupling of internal stabilizer for logic supply    |

| n.c.     | 19             | 17       | not connected                                         |

| VSSP2    | 20             | 13       | channel 2 negative power supply voltage               |

| OUT2     | 21             | 14       | channel 2 PWM output                                  |

| BOOT2    | 22             | 15       | channel 2 bootstrap capacitor                         |

| VDDP2    | 23             | 16       | channel 2 positive power supply voltage               |

| VSSA     | 24             | -        | negative analog supply voltage                        |

## 8. Functional description

#### 8.1 General

The TDA8953 is a two-channel audio power amplifier that uses Class D technology.

For each channel, the audio input signal is converted into a digital Pulse Width Modulation (PWM) signal using an analog input stage and a PWM modulator; see <u>Figure 1</u>. To drive the output power transistors, the digital PWM signal is fed to a control and handshake block and to high- and low-side driver circuits. This level-shifts the low-power digital PWM signal from a logic level to a high-power PWM signal switching between the main supply lines.

A second-order low-pass filter converts the PWM signal to an analog audio signal that can be used to drive a loudspeaker.

The TDA8953 single-chip Class D amplifier contains high-power switches, drivers, timing and handshaking between the power switches, along with some control logic. To ensure maximum system robustness, an advanced protection strategy has been implemented to provide overvoltage, overtemperature and overcurrent protection.

Each of the two audio channels contains a PWM modulator, an analog feedback loop and a differential input stage. The TDA8953 also contains circuits common to both channels such as the oscillator, all reference sources, the mode interface and a digital timing manager.

The two independent amplifier channels feature high output power, high efficiency, low distortion and low quiescent currents. They can be connected in the following configurations:

- Stereo Single-Ended (SE)

- Mono Bridge-Tied Load (BTL)

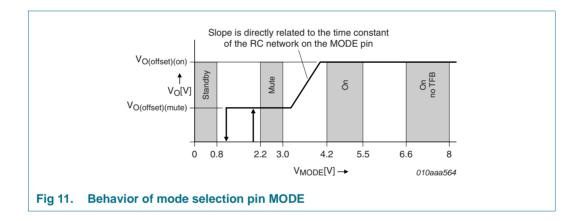

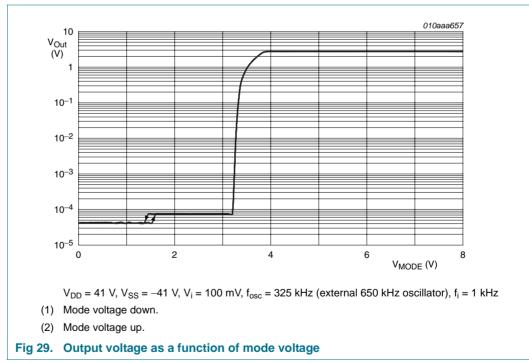

The amplifier system can be switched to one of three operating modes using pin MODE:

- · Standby mode: featuring very low quiescent current

- Mute mode: the amplifier is operational but the audio signal at the output is suppressed by disabling the voltage-to-current (VI) converter input stages

- Operating mode: the amplifier is fully operational, de-muted and can deliver an output signal

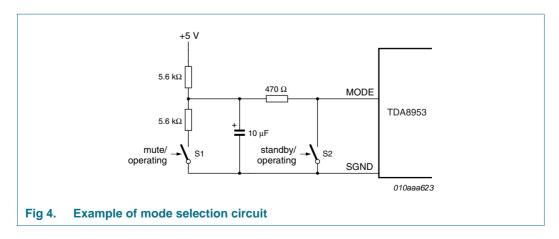

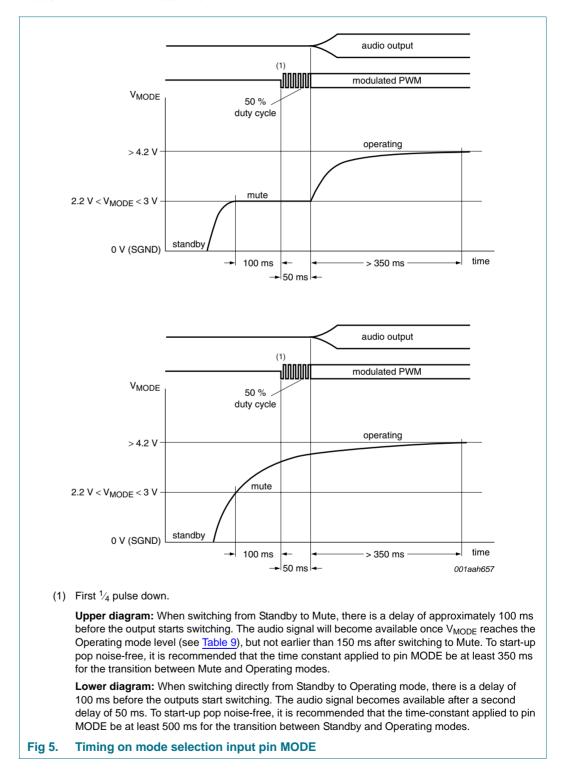

A slowly rising voltage should be applied (e.g. via an RC network) to pin MODE to ensure pop noise-free start-up. The bias-current setting of the (VI converter) input stages is related to the voltage on the MODE pin.

In Mute mode, the bias-current setting of the VI converters is zero (VI converters are disabled). In Operating mode, the bias current is at a maximum. The time constant required to apply the DC output offset voltage gradually between Mute and Operating mode levels can be generated using an RC network connected to pin MODE. An example of a circuit for driving the MODE pin, optimized for optimal pop noise performance, is shown in Figure 4. If the capacitor was omitted, the very short switching time constant could result in audible pop noises being generated at start-up (depending on the DC output offset voltage and loudspeaker used).

DA8953

The smooth transition between Mute and Operating modes causes a gradual increase in the DC offset output voltage, which becomes inaudible (no pop noise because the DC offset voltage rises smoothly). An overview of the start-up timing is provided in Figure 5. For proper switch-off, the MODE pin should be forced LOW at least 100 ms before the supply lines (V<sub>DD</sub> and V<sub>SS</sub>) drop below 12.5 V.

### 8.2 Pulse-width modulation frequency

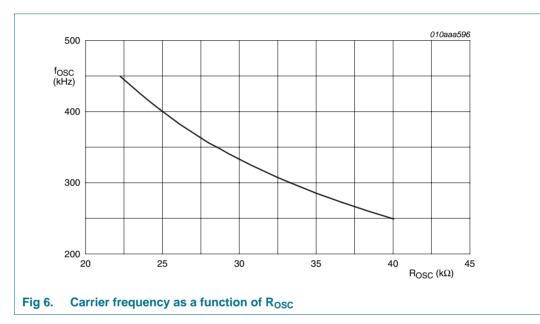

The amplifier output signal is a PWM signal with a typical carrier frequency of between 250 kHz and 450 kHz. A second-order LC demodulation filter on the output converts the PWM signal into an analog audio signal. The carrier frequency,  $f_{OSC}$ , is determined by an external resistor,  $R_{OSC}$ , connected between pins OSC and OSCREF. The optimal carrier frequency setting is between 250 kHz and 450 kHz.

The carrier frequency is set to 335 kHz by connecting an external 30 k $\Omega$  resistor between pins OSC and OSCREF (see Figure 6).

If two or more Class D amplifiers are used in the same audio application, an external clock circuit must be used to synchronize all amplifiers (see <u>Section 14.4</u>). This will ensure that they operate at the same switching frequency, thus avoiding beat tones (if the switching frequencies are different, audible interference known as 'beat tones' can be generated).

#### 8.3 Protection

The following protection circuits are incorporated into the TDA8953:

- Thermal protection:

- Thermal FoldBack (TFB)

- OverTemperature Protection (OTP)

- OverCurrent Protection (OCP)

- Window Protection (WP)

- Supply voltage protection:

- UnderVoltage Protection (UVP)

- OverVoltage Protection (OVP)

- UnBalance Protection (UBP)

- Clock Protection (CP)

How the device reacts to a fault condition depends on which protection circuit has been activated.

#### 8.3.1 Thermal protection

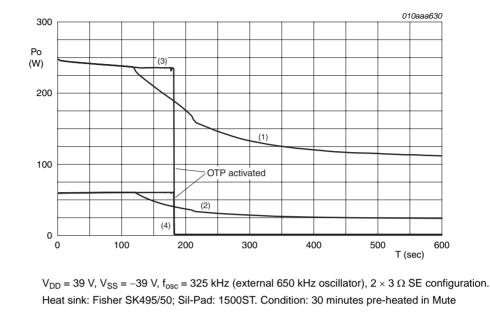

The TDA8953 employes an advanced thermal protection strategy. A TFB function gradually reduces the output power within a defined temperature range. If the temperature continues to rise, OTP is activated to shut the device down completely.

#### 8.3.1.1 Thermal FoldBack (TFB)

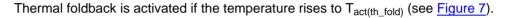

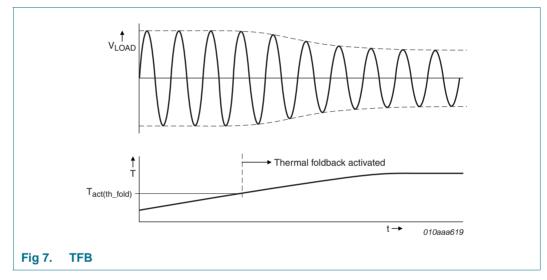

If the junction temperature  $(T_j)$  exceeds the thermal foldback activation threshold  $(T_{act(th_{fold})})$ , the gain is gradually reduced. This reduces the output signal amplitude and the power dissipation, eventually stabilizing the temperature.

Thermal foldback is active when:

$T_{act(th_{fold})} < T_{j} < T_{act(th_{prot})}$

The value of  $T_{act(th_{fold})}$  for the TDA8953 is approximately 145 °C; see <u>Table 9</u> for more details. The gain will be reduced by at least 6 dB (to  $T_{hg(th_{fold})}$ ) before the temperature reaches  $T_{act(th_{prot})}$  (see <u>Figure 8</u>).

TFB can be disabled by applying the appropriate voltage on pin MODE (see <u>Table 9</u>), in which case the dissipation will not be limited by TFB. The junction temperature may then rise as high as the OTP threshold, when the amplifier will be shut down (see <u>Section 8.3.1.2</u>). The amplifier will start up again once it has cooled down. This introduces audio holes.

#### 8.3.1.2 OverTemperature Protection (OTP)

If TFB fails to stabilize the temperature and the junction temperature continues to rise, the amplifier will shut down as soon as the temperature reaches the thermal protection activation threshold,  $T_{act(th_prot)}$ . The amplifier will resume switching approximately 100 ms after the temperature drops below  $T_{act(th_prot)}$ .

The thermal behavior is illustrated in Figure 8.

#### 8.3.2 OverCurrent Protection (OCP)

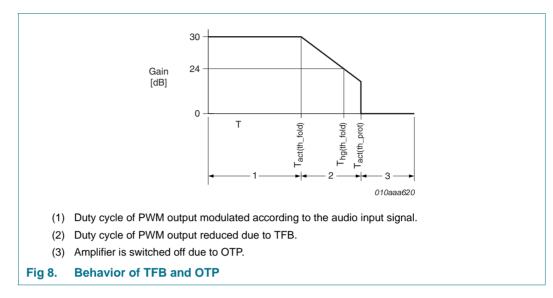

In order to guarantee the robustness of the TDA8953, the maximum output current delivered at the output stages is limited. OCP is built in for each output power switch.

OCP is activated when the current in one of the power transistors exceeds the OCP threshold ( $I_{ORM} = 12$  A) due, for example, to a short-circuit to a supply line or across the load.

The TDA8953 amplifier distinguishes between low-ohmic short-circuit conditions and other overcurrent conditions such as a dynamic impedance drop at the loudspeaker. The impedance threshold ( $Z_{th}$ ) depends on the supply voltage.

How the amplifier reacts to a short circuit depends on the short-circuit impedance:

- Short-circuit impedance > Z<sub>th</sub>: the amplifier limits the maximum output current to I<sub>ORM</sub> but the amplifier does not shut down the PWM outputs. Effectively, this results in a clipped output signal across the load (behavior very similar to voltage clipping).

- Short-circuit impedance < Z<sub>th</sub>: the amplifier limits the maximum output current to I<sub>ORM</sub> and at the same time discharges the capacitor on pin PROT. When C<sub>PROT</sub> is fully discharged, the amplifier shuts down completely and an internal timer is started.

The value of the protection capacitor ( $C_{PROT}$ ) connected to pin PROT can be between 10 pF and 220 pF (typically 47 pF). While OCP is activated, an internal current source is enabled that will discharge  $C_{PROT}$ .

When OCP is activated, the active power transistor is turned off and the other power transistor is turned on to reduce the current ( $C_{PROT}$  is partially discharged). Normal operation is resumed at the next switching cycle ( $C_{PROT}$  is recharged).  $C_{PROT}$  is partially discharge each time OCP is activated during a switching cycle. If the fault condition that caused OCP to be activated persists long enough to fully discharge  $C_{PROT}$ , the amplifier will switch off completely and a restart sequence will be initiated.

After a fixed period of 100 ms, the amplifier will attempt to switch on again, but will fail if the output current still exceeds the OCP threshold. The amplifier will continue trying to switch on every 100 ms. The average power dissipation will be low in this situation because the duty cycle is short.

Switching the amplifier on and off in this way will generate unwanted 'audio holes'. This can be avoided by increasing the value of  $C_{PROT}$  (up to 220 pF) to delay amplifier switch-off.  $C_{PROT}$  will also prevent the amplifier switching off due to transient frequency-dependent impedance drops at the speakers.

The amplifier will switch on, and remain in Operating mode, once the overcurrent condition has been removed. OCP ensures the TDA8953 amplifier is fully protected against short-circuit conditions while avoiding audio holes.

Table 4. Current limiting behavior during low output impedance conditions at different values of  $C_{PROT}$

| Туре    | $V_{DD}/V_{SS}$ (V) | V <sub>I</sub> (mV, p-p) |      |      | PWM output                       |                                    |                                  |

|---------|---------------------|--------------------------|------|------|----------------------------------|------------------------------------|----------------------------------|

|         |                     |                          |      | (pF) | Short<br>(Z <sub>th</sub> = 0 Ω) | Short<br>(Z <sub>th</sub> = 0.5 Ω) | Short<br>(Z <sub>th</sub> = 1 Ω) |

| TDA8953 | +41/-41             | 500                      | 20   | 10   | yes <sup>[1]</sup>               | yes[1]                             | yes <sup>[1]</sup>               |

|         |                     |                          | 1000 | 10   | yes                              | no                                 | no                               |

|         |                     |                          | 20   | 15   | yes <sup>[1]</sup>               | yes <mark>[1]</mark>               | yes <sup>[1]</sup>               |

|         |                     |                          | 1000 | 15   | yes                              | no                                 | no                               |

|         |                     |                          | 1000 | 220  | no                               | no                                 | no                               |

[1] OVP can be triggered by supply pumping; see Section 14.6.

When a short circuit occurs between the load and the supply voltage, the current will increase rapidly to  $I_{ORM}$ , when current limiting will be activated. If the short circuit condition persists long enough, the OCP circuit will shut down the amplifier. After the short circuit has been removed, the amplifier will resume normal operations (see Figure 9).

#### 8.3.3 Window Protection (WP)

Window Protection (WP) checks the conditions at the output terminals of the power stage and is activated:

• During the start-up sequence, when the TDA8953 is switching from Standby to Mute.

Start-up will be interrupted if a short-circuit is detected between one of the output terminals and one of the supply pins. The TDA8953 will wait until the short-circuit to the supply lines has been removed before resuming start-up. The short circuit will not generate large currents because the short-circuit check is carried out before the power stages are enabled.

• When the amplifier is shut down completely because the OCP circuit has detected a short circuit to one of the supply lines.

WP will be activated when the amplifier attempts to restart after 100 ms (see <u>Section 8.3.2</u>). The amplifier will not start-up again until the short circuit to the supply lines has been removed.

#### 8.3.4 Supply voltage protection

If the supply voltage drops below the minimum supply voltage threshold,  $V_{th(uvp)}$ , the UVP circuit will be activated and the system will shut down. Once the supply voltage rises above  $V_{th(uvp)}$  again, the system will restart after a delay of 100 ms.

If the supply voltage exceeds the maximum supply voltage threshold,  $V_{th(ovp)}$ , the OVP circuit will be activated and the power stages will be shut down. When the supply voltage drops below  $V_{th(ovp)}$  again, the system will restart after a delay of 100 ms.

An additional UnBalance Protection (UBP) circuit compares the positive analog supply voltage (on pin VDDA) with the negative analog supply voltage (on pin VSSA) and is triggered if the voltage difference exceeds a factor of two ( $V_{DDA} > 2 \times |V_{SSA}| \text{ OR } |V_{SSA}| > 2 \times V_{DDA}$ ). When the supply voltage difference drops below the unbalance threshold,  $V_{th(ubp)}$ , the system restarts after 100 ms.

#### 8.3.5 Clock protection (CP)

The clock signal can be provided by an external oscillator connected to pin OSC (see <u>Section 14.4</u>). When this signal is lost, or the clock frequency is too low, the amplifier will be switched off and will remain off until the clock signal has been restored.

#### 8.3.6 Overview of protection functions

An overview of all protection circuits and their respective effects on the output signal is provided in Table 5.

| Protection name    | Complete<br>shutdown | Restart directly | Restart after<br>100 ms | PROT pin active |

|--------------------|----------------------|------------------|-------------------------|-----------------|

| TFB <sup>[1]</sup> | Ν                    | Ν                | Ν                       | Ν               |

| OTP                | Y                    | Ν                | Y                       | Ν               |

| OCP                | Y[2]                 | N <sup>[2]</sup> | Y[2]                    | Y               |

| WP                 | N <mark>[3]</mark>   | Y                | Ν                       | Ν               |

| UVP                | Y                    | Ν                | Y                       | Ν               |

| OVP                | Y                    | Ν                | Y                       | Ν               |

| UBP                | Y                    | Ν                | Y                       | Ν               |

| CP                 | Y                    | Ν                | Y <u>[4]</u>            | Ν               |

Table 5.

Overview of TDA8953 protection circuits

[1] Amplifier gain depends on the junction temperature.

[2] The amplifier shuts down completely only if the short-circuit impedance is below the impedance threshold (Z<sub>th</sub>; see Section 8.3.2). In all other cases, current limiting results in a clipped output signal.

[3] Fault condition detected during any Standby-to-Mute transition or during a restart after OCP has been activated (short-circuit to one of the supply lines).

[4] As soon as the clock is present.

#### 8.4 Differential audio inputs

The audio inputs are fully differential ensuring a high common mode rejection ratio and maximum flexibility in the application.

- Stereo operation: to avoid supply pumping effects and to minimize peak currents in the power supply, the output stages should be configured in anti-phase. To avoid acoustical phase differences, the speakers should also be connected in anti-phase.

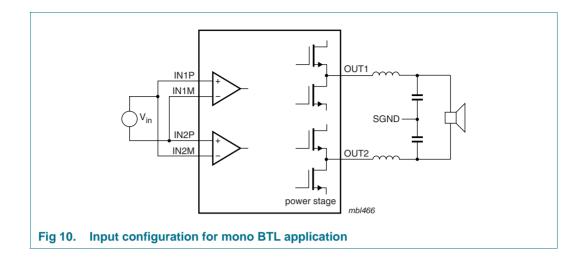

- Mono BTL operation: the inputs must be connected in anti-parallel. The output of one channel is inverted and the speaker load is connected between the two outputs of the TDA8953. In practice (because of the OCP threshold) the maximum output power in the BTL configuration can be boosted to twice the maximum output power available in the single-ended configuration.

The input configuration for a mono BTL application is illustrated in Figure 10.

$\mathbf{2}\times\mathbf{210}$  W class-D power amplifier

## 9. Internal circuitry

| Table 6.  | Internal circuit | try    |                                                                                                              |

|-----------|------------------|--------|--------------------------------------------------------------------------------------------------------------|

| Pin       |                  | Symbol | Equivalent circuit <sup>[1]</sup>                                                                            |

| TDA8953TH | H TDA8953J       |        |                                                                                                              |

| 7         | 1                | OSC    | 7 (1)<br>VDD<br>open: external clock<br>closed: internal clock<br>closed: internal clock<br>vSS<br>010aaa589 |

| 11        | 5                | OSCREF | 11 (5) — <sup>2 Ω</sup> V <sub>SS</sub><br>010aaa590                                                         |

| 13        | 7                | PROT   | 13 (7)<br>$\downarrow$ 28 $\mu$ A<br>$\downarrow$ 28 $\mu$ A<br>$\downarrow$ 1.5 mA<br>$V_{SS}$<br>010aaa592 |

| 4         | 21               | IN2M   |                                                                                                              |

| 5         | 22               | IN2P   | $5, 8 \xrightarrow{2 \text{ k}\Omega}$                                                                       |

| 8         | 2                | IN1P   |                                                                                                              |

| 9         | 3                | IN1M   | SGND<br>4, 9<br>(21, 3)<br>$2 \text{ k}\Omega$<br>$2 \text{ k}\Omega$<br>010aaa593<br>010aaa593              |

### $\mathbf{2}\times\mathbf{210}$ W class-D power amplifier

| Pin       |          | Symbol | Equivalent circuit <sup>[1]</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------|----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDA8953TH | TDA8953J |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6         | 23       | MODE   | 6 (23)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|           |          |        | SGND $$ gain (mute $\rightarrow$ on)<br>TFB on<br>$$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ |

| 1         | 18       | VSSA   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2         | 19       | SGND   | 14, 23 (8, 16)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3         | 20       | VDDA   | 2 (20) 15, 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14        | 8        | VDDP1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 15        | 9        | BOOT1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 16        | 10       | OUT1   | 2 (19) 16, 21<br>(10, 14)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 17        | 11       | VSSP1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 18        | 12       | STABI  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 20        | 13       | VSSP2  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 21        | 14       | OUT2   | (11, 13)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 22        | 15       | BOOT2  | 010aaa595                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 23        | 16       | VDDP2  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

#### Table 6. Internal circuitry ...continued

[1] Pin numbers in brackets are for the TDA8953J

## **10. Limiting values**

#### Table 7. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol                | Parameter                       | Conditions                                            | Min   | Max      | Unit |

|-----------------------|---------------------------------|-------------------------------------------------------|-------|----------|------|

| ΔV                    | voltage difference              | $V_{DD} - V_{SS}$ ; Standby, Mute modes               | -     | 90       | V    |

| I <sub>ORM</sub>      | repetitive peak output current  | maximum output current limiting; one channel driven   | 12    | -        | A    |

| T <sub>stg</sub>      | storage temperature             |                                                       | -55   | +150     | °C   |

| T <sub>amb</sub>      | ambient temperature             |                                                       | -40   | +85      | °C   |

| Tj                    | junction temperature            |                                                       | -     | 150      | °C   |

| V <sub>OSC</sub>      | voltage on pin OSC              | relative to V <sub>SSA</sub>                          | 0     | SGND + 6 | V    |

| VI                    | input voltage                   | referenced to SGND; on pins IN1P, IN1M, IN2P and IN2M | -5    | +5       | V    |

| V <sub>PROT</sub>     | voltage on pin PROT             | referenced to voltage on pin VSSA                     | 0     | 12       | V    |

| V <sub>MODE</sub>     | voltage on pin MODE             | referenced to SGND                                    | 0     | 8        | V    |

| V <sub>ESD</sub>      | electrostatic discharge voltage | Human Body Model (HBM)                                | -2000 | +2000    | V    |

|                       |                                 | Charged Device Model (CDM)                            | -500  | +500     | V    |

| V <sub>PWM(p-p)</sub> | peak-to-peak PWM voltage        | on pins OUT1 and OUT2                                 | -     | 120      | V    |

## **11. Thermal characteristics**

| Table 8.             | Thermal characteristics                     |             |     |      |

|----------------------|---------------------------------------------|-------------|-----|------|

| Symbol               | Parameter                                   | Conditions  | Тур | Unit |

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | in free air | 40  | K/W  |

| R <sub>th(j-c)</sub> | thermal resistance from junction to case    |             | 0.9 | K/W  |

## **12. Static characteristics**

#### Table 9. Static characteristics

$V_{DD} =$  41 V;  $V_{SS} =$  -41 V;  $f_{osc} =$  335 kHz;  $T_{amb} =$  25 °C; unless otherwise specified.

| Symbol                 | Parameter                                    | Conditions                                                           |            | Min   | Тур | Max   | Unit |

|------------------------|----------------------------------------------|----------------------------------------------------------------------|------------|-------|-----|-------|------|

| Supply                 |                                              |                                                                      |            |       |     |       |      |

| V <sub>DD</sub>        | positive supply voltage                      | Operating mode                                                       | <u>[1]</u> | 12.5  | 41  | 42.5  | V    |

| V <sub>SS</sub>        | negative supply voltage                      | Operating mode                                                       | [2]        | -12.5 | -41 | -42.5 | V    |

| V <sub>th(ovp)</sub>   | overvoltage protection<br>threshold voltage  | Standby, Mute modes; $V_{DD} - V_{SS}$                               |            | 85    | -   | 90    | V    |

| V <sub>th(uvp)</sub>   | undervoltage protection<br>threshold voltage | $V_{DD} - V_{SS}$                                                    |            | 20    | -   | 25    | V    |

| V <sub>th(ubp)</sub>   | unbalance protection threshold voltage       |                                                                      | [3]        | -     | 33  | -     | %    |

| I <sub>DD(tot)</sub>   | total positive supply current                | the sum of the currents through pins VDDA, VDDP1 and VDDP2           |            | -     | 50  | 60    | mA   |

|                        |                                              | Operating mode; no load; no filter; no RC-snubber network connected; |            |       |     |       |      |

| I <sub>SS(tot)</sub>   | total negative supply current                | the sum of the currents through pins VSSA, VSSP1 and VSSP2           |            | -     | 65  | 75    | mA   |

|                        |                                              | Operating mode; no load; no filter; no RC-snubber network connected; |            |       |     |       |      |

| I <sub>stb</sub>       | standby current                              |                                                                      |            | -     | 490 | 650   | μA   |

| Mode sele              | ect input; pin MODE                          |                                                                      |            |       |     |       |      |

| V <sub>MODE</sub>      | voltage on pin MODE                          | referenced to SGND                                                   | <u>[4]</u> | 0     | -   | 8     | V    |

|                        |                                              | Standby mode                                                         | [4][5]     | 0     | -   | 0.8   | V    |

|                        |                                              | Mute mode                                                            | [4][5]     | 2.2   | -   | 3.0   | V    |

|                        |                                              | Operating mode                                                       | [4][5]     | 4.2   | -   | 5.5   | V    |

|                        |                                              | Operating mode without TFB                                           | [4][5]     | 6.6   | -   | 8     |      |

| I                      | input current                                | V <sub>I</sub> = 5.5 V                                               |            | -     | 110 | 150   | μA   |

| Audio inp              | uts; pins IN1M, IN1P, IN2P and I             | N2M                                                                  |            |       |     |       |      |

| VI                     | input voltage                                | DC input                                                             | [4]        | -     | 0   | -     | V    |

| Amplifier              | outputs; pins OUT1 and OUT2                  |                                                                      |            |       |     |       |      |

| V <sub>O(offset)</sub> | output offset voltage                        | SE; Mute mode                                                        |            | -37   | -   | +37   | mV   |

| . ,                    |                                              | SE; Operating mode                                                   | [6]        | -150  | -   | +150  | mV   |

|                        |                                              | BTL; Mute mode                                                       |            | -30   | -   | +30   | mV   |

|                        |                                              | BTL; Operating mode                                                  | [6]        | -210  | -   | +210  | mV   |

| Stabilizer             | output; pin STABI                            |                                                                      |            |       |     |       |      |

| V <sub>O(STABI)</sub>  | output voltage on pin STABI                  | Mute and Operating modes; with respect to VSSA                       |            | 9.5   | 10  | 10.5  | V    |

| Symbol                    | Parameter                                 | Conditions                       | Min | Тур | Max | Unit |

|---------------------------|-------------------------------------------|----------------------------------|-----|-----|-----|------|

| Temperatu                 | re protection                             |                                  |     |     |     |      |

| $T_{act(th\_fold)}$       | thermal foldback activation temperature   | V <sub>MODE</sub> < 5.5 V        | -   | 145 | -   | °C   |

| $T_{hg(th_{fold})}$       | thermal foldback half gain temperature    | $V_{MODE}$ < 5.5 V; gain = 24 dB | -   | 153 | -   | °C   |

| T <sub>act(th_prot)</sub> | thermal protection activation temperature |                                  | -   | 154 | -   | °C   |

#### Table 9. Static characteristics ... continued

$V_{DD} = 41 \text{ V}; V_{SS} = -41 \text{ V}; f_{osc} = 335 \text{ kHz}; T_{amb} = 25 \text{ °C}; unless otherwise specified.}$

[1]  $V_{DD}$  is the supply voltage on pins VDDP1, VDDP2 and VDDA.

[2]  $V_{SS}$  is the supply voltage on pins VSSP1, VSSP2 and VSSA.

[3] Unbalance protection activated when  $V_{DDA} > 2 \times |V_{SSA}|$  OR  $|V_{SSA}| > 2 \times V_{DDA}$ .

[4] With respect to SGND (0 V).

[5] The transition between Standby and Mute modes has hysteresis, while the slope of the transition between Mute and Operating modes is determined by the time-constant of the RC network on pin MODE; see Figure 11.

[6] DC output offset voltage is gradually applied to the output during the transition between Mute and Operating modes. The slope caused by any DC output offset is determined by the time-constant of the RC network on pin MODE.

## **13. Dynamic characteristics**

### **13.1 Switching characteristics**

#### Table 10. Dynamic characteristics

$V_{DD}$  = 41 V;  $V_{SS}$  = -41 V;  $T_{amb}$  = 25 °C; unless otherwise specified.

| Symbol                                                   | Parameter                    | Conditions                       |     | Min        | Тур        | Мах      | Unit |  |  |  |  |

|----------------------------------------------------------|------------------------------|----------------------------------|-----|------------|------------|----------|------|--|--|--|--|

| Internal of                                              | Internal oscillator          |                                  |     |            |            |          |      |  |  |  |  |

| fosc(typ)                                                | typical oscillator frequency | $R_{OSC}$ = 30.0 k $\Omega$      |     | 290        | 335        | 365      | kHz  |  |  |  |  |

| f <sub>osc</sub>                                         | oscillator frequency         |                                  |     | 250        | -          | 450      | kHz  |  |  |  |  |

| External oscillator input or frequency tracking; pin OSC |                              |                                  |     |            |            |          |      |  |  |  |  |

| V <sub>OSC</sub>                                         | voltage on pin OSC           | HIGH-level                       |     | SGND + 4.5 | SGND + 5   | SGND + 6 | V    |  |  |  |  |

| V <sub>trip</sub>                                        | trip voltage                 |                                  |     | -          | SGND + 2.5 | -        | V    |  |  |  |  |

| f <sub>track</sub>                                       | tracking frequency           |                                  | [1] | 500        | -          | 1000     | kHz  |  |  |  |  |

| Zi                                                       | input impedance              |                                  |     | 1          | -          | -        | MΩ   |  |  |  |  |

| Ci                                                       | input capacitance            |                                  |     | -          | -          | 15       | pF   |  |  |  |  |

| t <sub>r(i)</sub>                                        | input rise time              | from SGND + 0 V to<br>SGND + 5 V | [2] | -          | -          | 100      | ns   |  |  |  |  |

[1] When using an external oscillator, the frequency f<sub>track</sub> (500 kHz minimum, 1000 kHz maximum) will result in a PWM frequency f<sub>osc</sub> (250 kHz minimum, 500 kHz maximum) due to the internal clock divider; see Section 8.2.

[2] When  $t_{r(i)}$  > 100 ns, the output noise floor will increase.

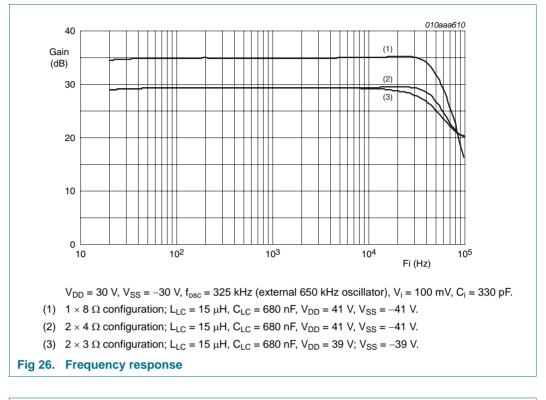

#### 13.2 Stereo SE configuration characteristics

#### Table 11. Dynamic characteristics

| Symbol                      | Parameter                                  | Conditions                                                       |      | Min  | Тур  | Мах | Unit |

|-----------------------------|--------------------------------------------|------------------------------------------------------------------|------|------|------|-----|------|

| P <sub>o</sub> output power | output power                               | L = 15 $\mu$ H; C <sub>LC</sub> = 680 nF; T <sub>j</sub> = 85 °C | [2]  |      |      |     |      |

|                             |                                            | THD = 0.5 %; $R_L$ = 4 $\Omega$                                  |      | -    | 160  | -   | W    |

|                             | THD = 10 %; $R_L$ = 4 $\Omega$             |                                                                  | -    | 210  | -    | W   |      |

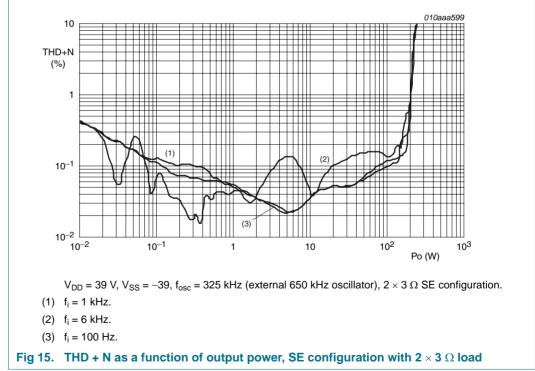

|                             |                                            | THD = 10 %; R <sub>L</sub> = 3 $\Omega$ ; V <sub>P</sub> = ±39 V | [3]  | -    | 235  | -   | W    |

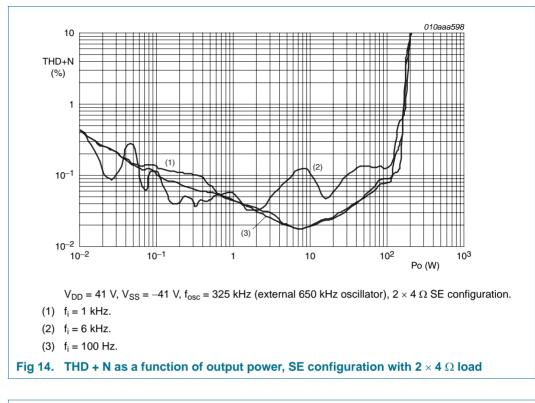

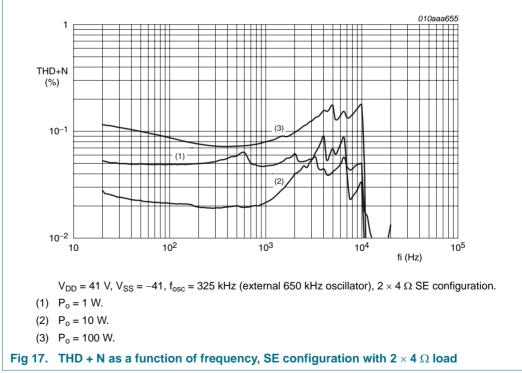

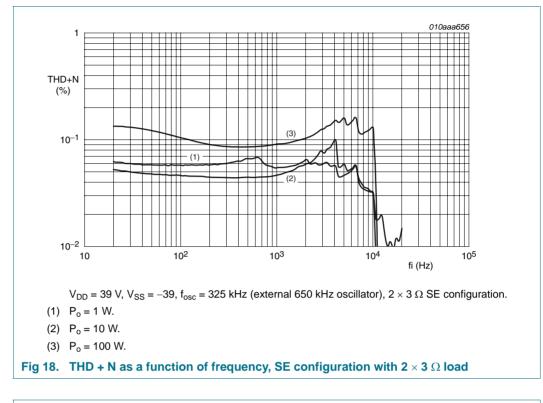

| THD                         | total harmonic distortion                  | $P_{o} = 1 \text{ W}; f_{i} = 1 \text{ kHz}$                     | [4]  | -    | 0.03 | 0.1 | %    |

|                             | $P_o = 1 W; f_i = 6 \text{ kHz}$           | [4]                                                              | -    | 0.05 | -    | %   |      |

| G <sub>v(cl)</sub>          | closed-loop voltage gain                   |                                                                  |      | 29   | 30   | 31  | dB   |

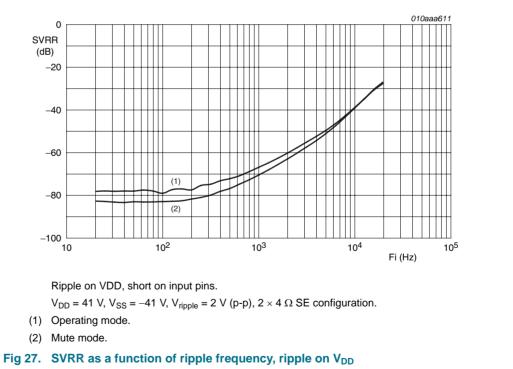

| SVRR                        | supply voltage rejection ratio             | between pins VDDPn and SGND                                      |      |      |      |     |      |

|                             |                                            | Operating mode; f <sub>i</sub> = 100 Hz                          | [5]  | -    | 90   | -   | dB   |

|                             |                                            | Operating mode; f <sub>i</sub> = 1 kHz                           | [5]  | -    | 70   | -   | dB   |

|                             |                                            | Mute mode; $f_i = 100 \text{ Hz}$                                | [5]  | -    | 75   | -   | dB   |

|                             |                                            | Standby mode; f <sub>i</sub> = 100 Hz                            | [5]  | -    | 120  | -   | dB   |

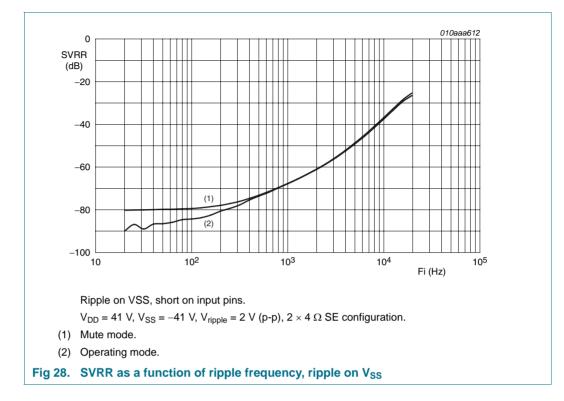

|                             |                                            | between pins VSSPn and SGND                                      |      |      |      |     |      |

|                             |                                            | Operating mode; f <sub>i</sub> = 100 Hz                          | [5]  | -    | 80   | -   | dB   |

|                             |                                            | Operating mode; f <sub>i</sub> = 1 kHz                           | [5]  | -    | 60   | -   | dB   |

|                             |                                            | Mute mode; $f_i = 100 \text{ Hz}$                                | [5]  | -    | 80   | -   | dB   |

|                             |                                            | Standby mode; f <sub>i</sub> = 100 Hz                            | [5]  | -    | 115  | -   | dB   |

| Zi                          | input impedance                            | between an input pin and SGND                                    |      | 45   | 56   | -   | kΩ   |

| V <sub>n(o)</sub>           | output noise voltage                       | Operating mode; inputs shorted                                   | [6]  | -    | 160  | -   | μV   |

|                             |                                            | Mute mode                                                        | [7]  | -    | 85   | -   | μV   |

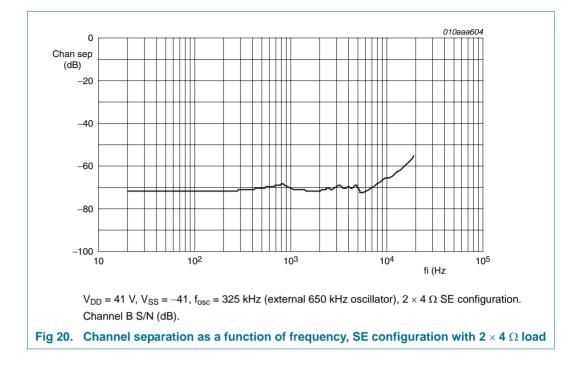

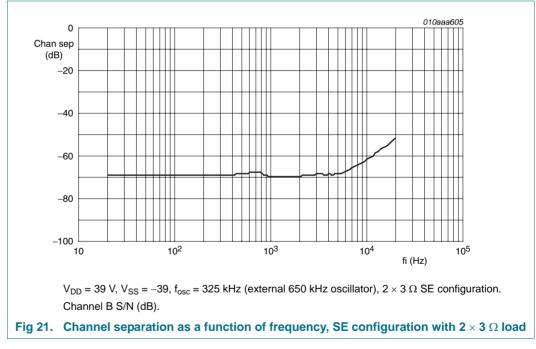

| $\alpha_{cs}$               | channel separation                         |                                                                  | [8]  | -    | 70   | -   | dB   |

| $ \Delta G_v $              | voltage gain difference                    |                                                                  |      | -    | -    | 1   | dB   |

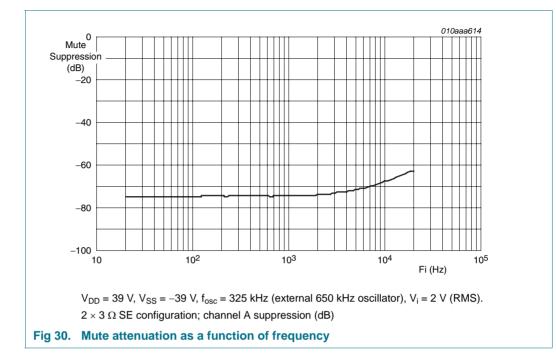

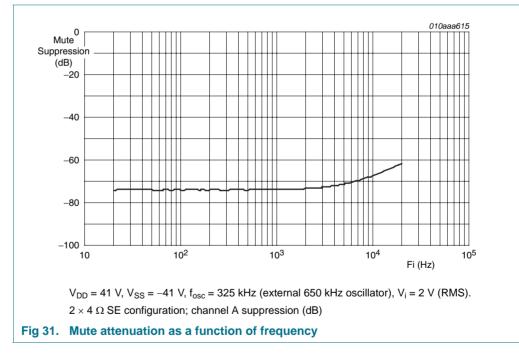

| $\alpha_{mute}$             | mute attenuation                           | $f_i = 1 \text{ kHz}; V_i = 2 \text{ V} (\text{RMS})$            | [9]  | -    | 75   | -   | dB   |

| CMRR                        | common mode rejection ratio                | $V_{i(CM)} = 1 V (RMS)$                                          |      | -    | 75   | -   | dB   |

| η <sub>po</sub>             | output power efficiency                    | SE, $R_L = 4 \Omega$                                             |      | -    | 93   | -   | %    |

|                             |                                            | SE, $R_L = 3 \Omega$                                             |      | -    | 90   | -   | %    |

|                             |                                            | BTL, $R_L = 8 \Omega$                                            |      | -    | 93   | -   | %    |

| R <sub>DSon(hs)</sub>       | high-side drain-source on-state resistance |                                                                  | [10] | -    | 110  | -   | mΩ   |

| R <sub>DSon(Is)</sub>       | low-side drain-source on-state resistance  |                                                                  | [10] | -    | 105  | -   | mΩ   |

[1] R<sub>sL</sub> is the series resistance of the low-pass LC filter inductor used in the application.

[2] Output power is measured indirectly; based on R<sub>DSon</sub> measurement; see <u>Section 14.3</u>.

[3] One channel driven at maximum output power; the other channel driven at one eight maximum output power.

[4] THD measured between 22 Hz and 20 kHz, using AES17 20 kHz brick wall filter.

[5] V<sub>ripple</sub> = V<sub>ripple(max)</sub> = 2 V (p-p); measured independently between VDDPn and SGND and between VSSPn and SGND.

[6] 22 Hz to 20 kHz, using AES17 20 kHz brick wall filter.

[7] 22 Hz to 20 kHz, using AES17 20 kHz brick wall filter.

[8]  $P_o = 1$  W;  $f_i = 1$  kHz.

[9]  $V_i = V_{i(max)} = 1 V (RMS); f_i = 1 kHz.$

[10] Leads and bond wires included.

#### 13.3 Mono BTL application characteristics

#### Table 12. Dynamic characteristics

| Symbol              | Parameter                      | Conditions                                                         |     | Min | Тур  | Max | Unit |

|---------------------|--------------------------------|--------------------------------------------------------------------|-----|-----|------|-----|------|

| Po                  | output power                   | $T_j$ = 85 °C; $L_{LC}$ = 15 µH; $C_{LC}$ = 680 nF (see Figure 13) | [2] |     |      |     |      |

|                     |                                | THD = 0.5 %; $R_L$ = 8 $\Omega$                                    |     | -   | 330  | -   | W    |

|                     |                                | THD = 10 %; $R_L$ = 8 $\Omega$                                     |     | -   | 420  | -   | W    |

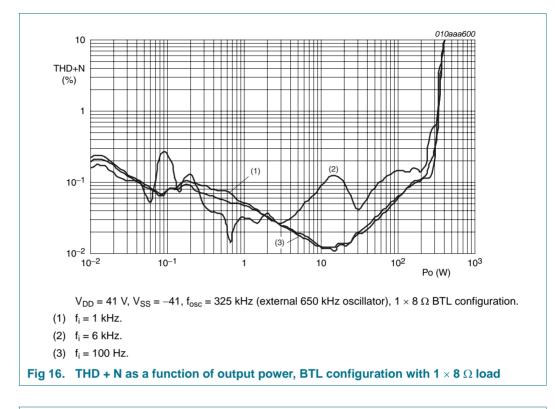

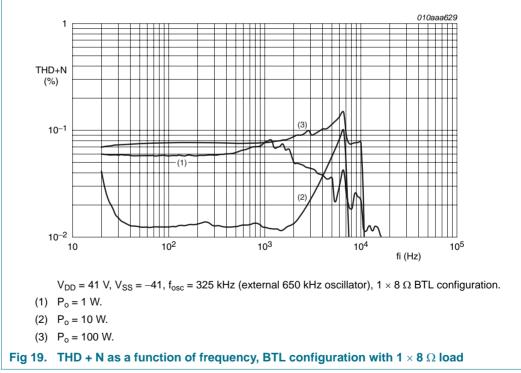

| THD                 | total harmonic distortion      | $P_{o} = 1 W; f_{i} = 1 kHz$                                       | [3] | -   | 0.03 | 0.1 | %    |

|                     |                                | $P_{o} = 1 W; f_{i} = 6 kHz$                                       | [3] | -   | 0.05 | -   | %    |

| G <sub>v(cl)</sub>  | closed-loop voltage gain       |                                                                    |     | -   | 36   | -   | dB   |

| SVRR                | supply voltage rejection ratio | between pin VDDPn and SGND                                         |     |     |      |     |      |

|                     |                                | Operating mode; f <sub>i</sub> = 100 Hz                            | [5] | -   | 80   | -   | dB   |

|                     |                                | Operating mode; f <sub>i</sub> = 1 kHz                             | [5] | -   | 80   | -   | dB   |

|                     |                                | Mute mode; $f_i = 100 \text{ Hz}$                                  | [5] | -   | 95   | -   | dB   |

|                     |                                | Standby mode; f <sub>i</sub> = 100 Hz                              | [5] | -   | 120  | -   | dB   |

|                     |                                | between pin VSSPn and SGND                                         |     |     |      |     |      |

|                     |                                | Operating mode; f <sub>i</sub> = 100 Hz                            | [5] | -   | 75   | -   | dB   |

|                     |                                | Operating mode; f <sub>i</sub> = 1 kHz                             | [5] | -   | 75   | -   | dB   |

|                     |                                | Mute mode; $f_i = 100 \text{ Hz}$                                  | [5] | -   | 90   | -   | dB   |

|                     |                                | Standby mode; f <sub>i</sub> = 100 Hz                              | [5] | -   | 130  | -   | dB   |

| Z <sub>i</sub>      | input impedance                | measured between one of the input pins and SGND                    |     | 45  | 56   | -   | kΩ   |

| V <sub>n(o)</sub>   | output noise voltage           | Operating mode; inputs shorted                                     | [5] | -   | 190  | -   | μV   |

|                     |                                | Mute mode                                                          | [6] | -   | 45   | -   | μV   |

| $\alpha_{\sf mute}$ | mute attenuation               | f <sub>i</sub> = 1 kHz; V <sub>i</sub> = 2 V (RMS)                 | [7] | -   | 75   | -   | dB   |

| CMRR                | common mode rejection ratio    | $V_{i(CM)} = 1 V (RMS)$                                            |     | -   | 75   | -   | dB   |

|                     |                                |                                                                    |     |     |      |     |      |

[1]  $R_{sL}$  is the series resistance of the low-pass LC filter inductor used in the application.

[2] Output power is measured indirectly; based on R<sub>DSon</sub> measurement; see Section 14.3.

[3] THD measured between 22 Hz and 20 kHz, using AES17 20 kHz brick wall filter.

[4]  $V_{ripple} = V_{ripple(max)} = 2 V (p-p).$

[5] 22 Hz to 20 kHz, using an AES17 20 kHz brick wall filter; low noise due to BD modulation.

[6] 22 Hz to 20 kHz, using an AES17 20 kHz brick wall filter.

[7]  $V_i = V_{i(max)} = 1 V (RMS); f_i = 1 kHz.$

## 14. Application information

#### 14.1 Mono BTL application

When using the power amplifier in a mono BTL application, the inputs of the two channels must be connected in anti-parallel and the phase of one of the inputs must be inverted; see <u>Figure 10</u>. In principle, the loudspeaker can be connected between the outputs of the two single-ended demodulation filters.

#### 14.2 Pin MODE

To ensure a pop noise-free start-up, an RC time-constant must be applied to pin MODE. The bias-current setting of the VI converter input is directly related to the voltage on pin MODE. In turn the bias-current setting of the VI converters is directly related to the DC output offset voltage. A slow dV/dt on pin MODE results in a slow dV/dt for the DC output offset voltage, ensuring a pop noise-free transition between Mute and Operating modes. A time-constant of 500 ms is sufficient to guarantee pop noise-free start-up; see Figure 4, Figure 5 and Figure 11 for more information.

#### 14.3 Estimating the output power

#### 14.3.1 Single-Ended (SE)

Maximum output power:

$$P_{o(0.5\%)} = \frac{\left[\frac{R_L}{R_L + R_{DSon(hs)} + R_{s(L)}} \times 0.5(V_{DD} - V_{SS}) \times (1 - t_{w(min)} \times 0.5f_{osc})\right]^2}{2R_L}$$

(1)

Maximum output current is internally limited to 12 A:

$$I_{o(peak)} = \frac{0.5(V_{DD} - V_{SS}) \times (1 - t_{w(min)} \times 0.5f_{osc})}{R_L + R_{DSon(hs)} + R_{s(L)}}$$

(2)

Where:

- P<sub>o(0.5 %)</sub>: output power at the onset of clipping

- R<sub>L</sub>: load impedance

- R<sub>DSon(hs)</sub>: high-side R<sub>DSon</sub> of power stage output DMOS (temperature dependent)

- Rs(L): series impedance of the filter coil

- t<sub>w(min)</sub>: minimum pulse width (typical 150 ns; temperature dependent)

- fosc: oscillator frequency

**Remark:** Note that  $I_{o(peak)}$  should be less than 12 A (<u>Section 8.3.2</u>).  $I_{o(peak)}$  is the sum of the current through the load and the ripple current. The value of the ripple current is dependent on the coil inductance and the voltage drop across the coil.

#### 14.3.2 Bridge-Tied Load (BTL)

Maximum output power:

$$P_{o(0.5\%)} = \frac{\left[\frac{R_L}{R_L + R_{DSon(hs)} + R_{DSon(ls)}} \times (V_{DD} - V_{SS}) \times (1 - t_{w(min)} \times 0.5f_{osc})\right]^2}{2R_I}$$

(3)

Maximum output current internally limited to 12 A:

$$I_{o(peak)} = \frac{(V_{DD} - V_{SS}) \times (1 - t_{w(min)} \times 0.5 f_{osc})}{R_L + (R_{DSon(hs)} + R_{DSon(ls)}) + 2R_{s(L)}}$$

(4)

Where:

- P<sub>o(0.5 %)</sub>: output power at the onset of clipping

- R<sub>L</sub>: load impedance

- R<sub>DSon(hs)</sub>: high-side R<sub>DSon</sub> of power stage output DMOS (temperature dependent)

- R<sub>DSon(Is)</sub>: low-side R<sub>DSon</sub> of power stage output DMOS (temperature dependent)

- R<sub>s(L)</sub>: series impedance of the filter coil

- t<sub>w(min)</sub>: minimum pulse width (typical 150 ns, temperature dependent)

- f<sub>osc</sub>: oscillator frequency

**Remark:** Note that  $I_{o(peak)}$  should be less than 12 A; see <u>Section 8.3.2</u>.  $I_{o(peak)}$  is the sum of the current through the load and the ripple current. The value of the ripple current is dependent on the coil inductance and the voltage drop across the coil.

#### 14.4 External clock

To ensure duty cycle-independent operation, the external clock frequency is divided by two internally. The external clock frequency is therefore twice the internal clock frequency (typically  $2 \times 335$  kHz = 670 kHz).

If several Class D amplifiers are used in a single application, it is recommended that all the devices run at the same switching frequency. This can be achieved by connecting the OSC pins together and feeding them from an external oscillator. When using an external oscillator, it is necessary to force pin OSC to a DC level above SGND. This disables the internal oscillator and causes the PWM to switch at half the external clock frequency.

The internal oscillator requires an external resistor  $R_{OSC}$ , connected between pin OSC and pin OSCREF.  $R_{OSC}$  must be removed when using an external oscillator.

The noise generated by the internal oscillator is supply voltage dependent. An external low-noise oscillator is recommended for low-noise applications running at high supply voltages.

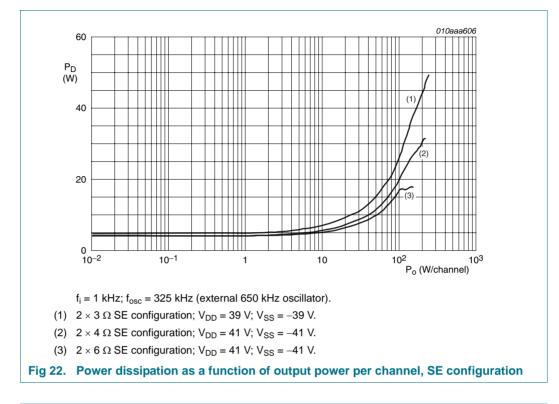

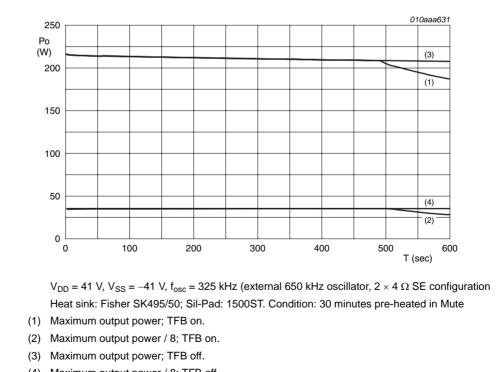

#### 14.5 Heatsink requirements

An external heatsink must be connected to the TDA8953.

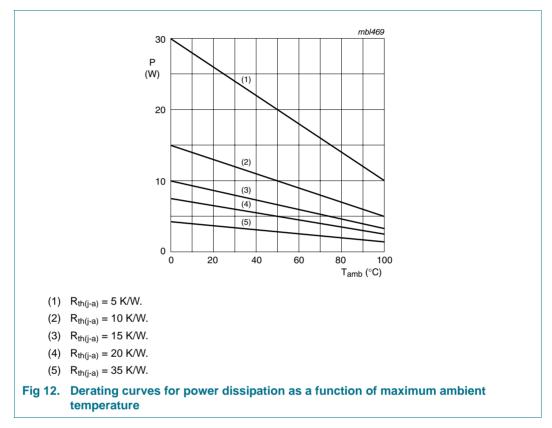

<u>Equation 5</u> defines the relationship between maximum power dissipation before activation of TFB and total thermal resistance from junction to ambient.

$$R_{th(j-a)} = \frac{T_j - T_{amb}}{P}$$

(5)

Power dissipation (P) is determined by the efficiency of the TDA8953.

In the following example, a heatsink calculation is made for an 4  $\Omega$  SE application with a  $\pm 30$  V supply:

The audio signal has a crest factor of 10 (the ratio between peak power and average power (20 dB); this means that the average output power is  $\frac{1}{10}$  of the peak power.

Thus, the peak RMS output power level is the 0.5 % THD level, i.e. 92.5 W per channel.

The average power is then  $\frac{1}{10} \times 92.5$  W = 9.25 W per channel.

The dissipated power at an output power of 9.25 W is approximately 9.5 W.

When the maximum expected ambient temperature is 50 °C, the total R<sub>th(j-a)</sub> becomes